基于Wishbone和端點IP的PCIE接口設計

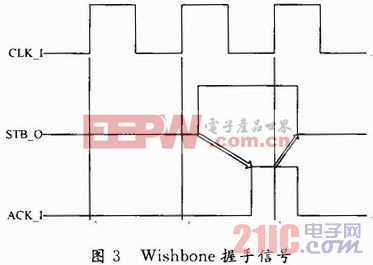

Wishbone數據傳輸的握手機制如圖3所示。準備傳輸數據時,Master設置STB_O輸出信號為有效(Wishbone設置高電平為有效電平),表示開始對Slave進行訪問;當接收完數據,Master的ACK_I信號接收到Slave發出的完成信號,然后Master取消STB_O信號。Slave可以置RTY_O為高,表示Slave現在忙,以后再試;還可以置ERR_O為高,表示出錯。在Master和Slave傳輸數據期間,兩端都可以控制數據的傳輸速度。本文引用地址:http://www.104case.com/article/190176.htm

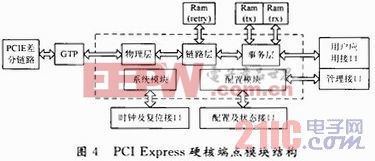

1.2 Xilinx集成硬核端點IP結構

Xilinx的端點IP符合PCIe協議V1.1,集成了PCI Express協議中的物理層(PHY)、數據鏈接層(DLL)和傳輸層(TLL),其結構框圖如圖4所示,包含有以下幾個接口:時鐘及復位接口;事務層接口;管理接口;緩存接口;收發器接口;配置和狀態接口。

事務層接口,與用戶應用設計連接。在本次設計中連接到Wishbone從接口。

時鐘及復位接口,包含DCM所需的反饋時鐘。在本次設計中系統參考時鐘為100 MHz,用戶時鐘為62.5MHz。

收發器接口,與GTP相連。包含多條發送和接收鏈路,每條鏈路包含一對發送和一對接收信號,發送和接收信號都是差分信號,本文采用X1。

緩存接口,與事務層和數據鏈路層相連。用來實現數據傳輸的緩沖。這三個緩存器已在CORE Generator中進行了例化和配置。Block RAM數據通路為64位寬。三個Block RAM接口均與端點模塊的其余部分同步運行。每個接口都具備單獨的讀寫地址、數據和控制信號。

管理接口,用于訪問端點模塊中的各種寄存器和信號,包括PCI Express配置空間、各種控制和狀態寄存器。管理接口還包含用于統計數據和監測的輸出信號以及一個讀取流量控制信用輸出的接口。

配置及狀態接口包含控制和狀態、錯誤、后端接口配置以及中斷端口。

收發器接口、存儲器接口以及時鐘和復位接口在CORE Generator封裝中自動連接。這些接口在封裝之外均不可見。

1.3 TLP包結構

PCI Express協議是基于TLP包傳輸的,在PCIExpress設備之間傳輸的TLP結構如圖5所示。數據發送時,來自軟件層/核心設備的核心信息包括頭以及數據部分(某些TLP不包含數據),經事務層添加摘要部分,發往數據鏈路層后附加序列號及LCRC,最后在物理層添加幀開始及結束標志后發送;數據接收時,逐層去掉附加部分,最后將頭及數據部分送至軟件層/核心設備。

評論