基于FPGA的數(shù)字頻率合成器設(shè)計(jì)與實(shí)現(xiàn)

2.2 存儲(chǔ)波形信號(hào)的ROM的設(shè)計(jì)

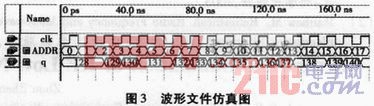

本模塊ROM的設(shè)計(jì),基于ALTERA公司的開放的IP核,自動(dòng)生成,其存儲(chǔ)的正弦波波形文件,即初始化文件,通過C語言編寫,生成波形數(shù)據(jù)存儲(chǔ)到ROM中。由于采用的DAC器件為8位輸入,因此本文設(shè)計(jì)的ROM數(shù)據(jù)寬度為8,不過為了提高精度,存儲(chǔ)器深度選為1024。仿真電路如圖3所示。本文引用地址:http://www.104case.com/article/190153.htm

2.3 系統(tǒng)整體模塊及仿真圖

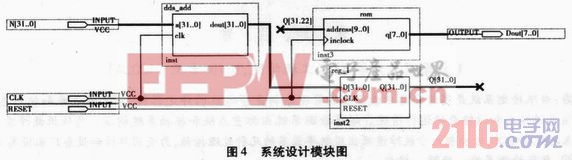

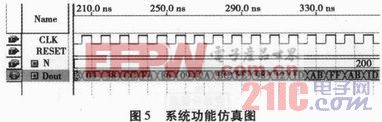

本系統(tǒng)整體電路圖如圖4所示,包括累加器、32位的寄存器、存儲(chǔ)波形的ROM三部分組成。其中累加器進(jìn)行DDS相位調(diào)節(jié),輸出的結(jié)果,送入32位的D觸發(fā)器,產(chǎn)生讀取ROM的地址信號(hào),由于受到ROM的限制,我們截取高10位作為讀取ROM的地址信號(hào),產(chǎn)生穩(wěn)定的信號(hào)。輸入后續(xù)的ADC及濾波電路進(jìn)行處理,輸出穩(wěn)定的波形。仿真電路如圖5所示。該系統(tǒng)很好地實(shí)現(xiàn)了波形數(shù)據(jù)的讀取。

3 結(jié)束語

本文在FPGA開發(fā)平臺(tái)上,基于DDS工作原理,用VerilogHDL語言設(shè)計(jì)并實(shí)現(xiàn)了DDS直接頻率合成,經(jīng)過D/A轉(zhuǎn)化和外加濾波整形電路處理波形數(shù)據(jù),輸出頻率可調(diào)的正弦波。可以作為信號(hào)源使用。具有較好的實(shí)用價(jià)值。

評(píng)論