基于CPLD的PLC背板總線協(xié)議接口芯片的設(shè)計

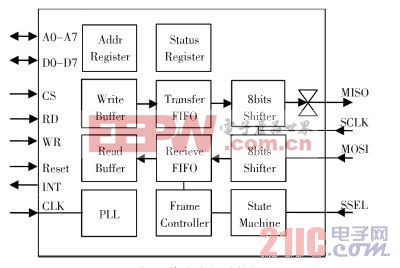

主機(jī)和從機(jī)協(xié)議芯片的內(nèi)部結(jié)構(gòu)框圖相同,如圖3 所示。

協(xié)議芯片內(nèi)部有狀態(tài)機(jī)控制器、幀控制器、移位寄存器、接收/發(fā)送FIFO 和讀寫緩存。單片機(jī)發(fā)送的周期性、非周期性數(shù)據(jù)幀,首先都寫到寫緩存,在發(fā)送FIFO 中進(jìn)行排隊發(fā)送,在SPI 時鐘SCLK 的驅(qū)動下數(shù)據(jù)幀被轉(zhuǎn)換為串行數(shù)據(jù)發(fā)送到背板總線;在SPI 時鐘的作用下, 接收來自背板總線上的串行數(shù)據(jù);在狀態(tài)機(jī)和幀控制器的協(xié)調(diào)下,接收FIFO 中的有效數(shù)據(jù)幀被提取并放進(jìn)讀緩存區(qū),等待單片機(jī)來讀取,如果是非周期性數(shù)據(jù)則發(fā)中斷信號通知單片機(jī)來取數(shù)據(jù)。讀緩存中的周期性數(shù)據(jù)是可以覆蓋的,新接收到的周期性數(shù)據(jù)直接覆蓋舊的周期性數(shù)據(jù),而非周期性數(shù)據(jù)是單獨存放的,不能覆蓋,由單片機(jī)讀取并清除。

圖3 協(xié)議芯片內(nèi)部結(jié)構(gòu)框圖

協(xié)議芯片使得外接的單片機(jī)可以在空閑的情況下訪問讀緩存和寫緩存,單片機(jī)不必頻繁地通過中斷技術(shù)處理周期性數(shù)據(jù),也使得PLC 主機(jī)可以無等待地訪問從機(jī)的周期性數(shù)據(jù)。

3 基于CPLD 的協(xié)議芯片實現(xiàn)

3.1 CPLD 芯片選型。

本設(shè)計選用lattice 公司的MachXO 系列芯片,該系列CPLD 集成了部分FPGA 的功能, 除了內(nèi)置豐富的LUT 資源以外,還有大量分布式的SRAM 位和嵌入式的專用于FIFO 設(shè)計的SRAM 塊, 并有模擬鎖相環(huán)(PLL)支持時鐘信號的倍頻、分頻等,I/O引腳可配置成1.2/1.5/1.8/3.3V 電平兼容。

評論