基于FPGA技術(shù)的RS 232接口時(shí)序電路設(shè)計(jì)

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述了如何通過(guò)FPGA實(shí)現(xiàn)RS 232接口的時(shí)序邏輯設(shè)計(jì)。

關(guān)鍵詞:FPGA;時(shí)序電路;RS 232;串行通信

0 引言

RS 232接口是1970年由美國(guó)電子工業(yè)協(xié)會(huì)(EIA)聯(lián)合貝爾系統(tǒng)、調(diào)制解調(diào)器廠家及計(jì)算機(jī)終端生產(chǎn)廠家共同制定的用于串行通信的標(biāo)準(zhǔn)。它的全名是“數(shù)據(jù)終端設(shè)備(DTE)和數(shù)據(jù)通信設(shè)備(DCE)之間串行二進(jìn)制數(shù)據(jù)交換接口技術(shù)標(biāo)準(zhǔn)”。該標(biāo)準(zhǔn)規(guī)定采用一個(gè)25個(gè)腳的DB25連接器,對(duì)連接器的每個(gè)引腳的信號(hào)內(nèi)容加以規(guī)定,還對(duì)各種信號(hào)的電平加以規(guī)定。隨著設(shè)備的不斷改進(jìn),出現(xiàn)了代替DB25的DB9接口,現(xiàn)在都把RS 232接口叫做DB9。RS 232接口是最常見(jiàn)的一種串行通信接口,普通PC機(jī)一般都具有此類接口,其最高通信速率(波特率)為115.2 Kb/s。采用9 600b/s進(jìn)行數(shù)據(jù)傳輸交換的應(yīng)用較多。通過(guò)FPGA實(shí)現(xiàn)其時(shí)序電路,主要完成發(fā)送和接收兩部分邏輯電路的設(shè)計(jì)。

1 發(fā)送邏輯電路的設(shè)計(jì)

1.1 時(shí)序近似

RS 232接口可選的波特率如9 600b/s,115.2 Kb/s等同11.059 2 MHz的時(shí)鐘有著整數(shù)倍的關(guān)系,但通常情況下提供FPGA的時(shí)鐘大多采用頻率為40~80 MHz,同11.059 2 MHz之間存在一定的時(shí)序誤差。

例如一個(gè)由1個(gè)起始位,8個(gè)數(shù)據(jù)位,1個(gè)停止位組成,假定串行信號(hào)的波特率為9 600b/s,則每個(gè)位的時(shí)序時(shí)間為:

104 166.666 666 666 666 666 666 666 666 67 ns

相當(dāng)于80 MHz計(jì)數(shù)器計(jì)數(shù)到:

8 333.333 333 333 333 333 333 333 333 333 3舍去小數(shù)部分。

由80 MHz驅(qū)動(dòng)的計(jì)數(shù)器產(chǎn)生時(shí)序時(shí)每個(gè)字符誤差為4.166 666 666 666 666 666 666 666 666 666 7 ns。這樣由10個(gè)字符組成的一次發(fā)射時(shí)序誤差約為41.7 ns小于1/1 000可以忽略不計(jì)。

1.2 發(fā)送時(shí)序設(shè)計(jì)

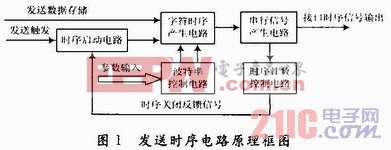

RS 232接口的時(shí)序電路由啟動(dòng)電路、字符產(chǎn)牛電路、同步時(shí)鐘產(chǎn)生電路。波特率控制電路,和時(shí)序關(guān)閉電路組成。發(fā)送時(shí)序電路原理框圖如圖1所示。

1.3 發(fā)送電路原理描述

以波特率為9 600b/s的時(shí)序?yàn)槔诎l(fā)送數(shù)據(jù)之前,系統(tǒng)微處理器將相應(yīng)波特率參數(shù)鎖存在FPGA內(nèi)部的波特率控制電路的寄存器內(nèi)(由觸發(fā)器構(gòu)建),使每次輸出的字符同步信號(hào)的周期為104.167μs(對(duì)應(yīng)波特率9 600b/s)。

當(dāng)系統(tǒng)發(fā)出發(fā)送啟動(dòng)信號(hào)時(shí),字符時(shí)序電路以每個(gè)字符104.167μs的速率在預(yù)發(fā)射數(shù)據(jù)的邏輯電平控制之下輸出時(shí)序信號(hào),同時(shí)在時(shí)序中插入停止位和起始位字符信號(hào)。

在完成上述發(fā)送時(shí)序的過(guò)程中,時(shí)序計(jì)數(shù)控制電路會(huì)檢測(cè)發(fā)送時(shí)序的工作狀態(tài),當(dāng)檢測(cè)每次時(shí)序的停止位完成輸出后,時(shí)序計(jì)數(shù)控制電路會(huì)發(fā)出時(shí)序關(guān)閉反饋信號(hào),使電路回復(fù)到預(yù)發(fā)射的初始工作狀態(tài),并等待處理器再次觸發(fā)時(shí)序電路和對(duì)數(shù)據(jù)參數(shù)的重置。

2 接收邏輯電路的設(shè)計(jì)

2.1 接收時(shí)序設(shè)計(jì)

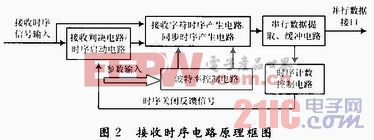

接收時(shí)序電路原理框圖如圖2所示。

2.2 接收電路原理描述

以波特率為9 600b/s的時(shí)序?yàn)槔诮邮諗?shù)據(jù)之前系統(tǒng)微處理器將相應(yīng)波特率參數(shù)鎖存在FPGA內(nèi)部的波特率控制電路的寄存器內(nèi)(由觸發(fā)器構(gòu)建),使每次輸出的字符位同步信號(hào)的周期為104.167 μs(對(duì)應(yīng)波特率9 600b/s)。字符位同步信號(hào)是接收電路存儲(chǔ)接收數(shù)據(jù)邏輯狀態(tài)的關(guān)鍵。作為同步時(shí)鐘信號(hào),該信號(hào)可驅(qū)動(dòng)接收到的串行數(shù)據(jù)電平輸入移位寄存器內(nèi)并鎖存。

當(dāng)系統(tǒng)接收到一幀串行信號(hào)時(shí),首先要判斷是否是新的一幀數(shù)據(jù),接收判決電路通過(guò)對(duì)輸入串行信號(hào)的起始位字符脈寬進(jìn)行裁決,按照RS 232接口通信協(xié)議在某一特性波特率下,一幀信號(hào)的起始是一定脈寬的負(fù)脈沖。通過(guò)計(jì)數(shù)器可以檢測(cè)到負(fù)脈沖的起始時(shí)間和脈沖寬度,當(dāng)脈沖寬度達(dá)到某一數(shù)值時(shí)啟動(dòng)接收時(shí)序。

接收時(shí)序電路會(huì)通過(guò)被記錄下的接收信號(hào)的準(zhǔn)確到達(dá)時(shí)間,推算出每個(gè)串行數(shù)據(jù)位對(duì)應(yīng)的時(shí)序時(shí)刻,從而輸出對(duì)應(yīng)每個(gè)位中間時(shí)刻的字符位同步信號(hào)(脈沖)作為接收移位寄存器的同步時(shí)鐘信號(hào)驅(qū)動(dòng)移位寄存器對(duì)接收數(shù)據(jù)電平的記錄。

被鎖存的數(shù)據(jù)通過(guò)并行總線被系統(tǒng)微處理器提取。這一過(guò)程可以通過(guò)對(duì)處理器的中斷實(shí)現(xiàn),但需要接收時(shí)序電路在完成數(shù)據(jù)接收后立即產(chǎn)生一個(gè)中斷信號(hào),通知處理器提取接收數(shù)據(jù)。

接收時(shí)序計(jì)數(shù)器會(huì)對(duì)接收時(shí)序時(shí)間進(jìn)行檢測(cè),當(dāng)接收時(shí)序到達(dá)結(jié)束時(shí)刻時(shí),其輸出的時(shí)序關(guān)閉反饋信號(hào)會(huì)使接收電路恢復(fù)到初始工作電路,等待下一幀數(shù)據(jù)的到達(dá)。

3 結(jié)論

通過(guò)FPGA實(shí)現(xiàn)RS 232接口時(shí)序邏輯電路,已經(jīng)在工程實(shí)踐過(guò)程中實(shí)現(xiàn)了接口標(biāo)準(zhǔn)規(guī)定的全部功能。可以認(rèn)為,通過(guò)FPGA的邏輯電路設(shè)計(jì)可以完全取代專用芯片。介于FPGA的可塑性和靈活性,可以通過(guò)相應(yīng)邏輯電路設(shè)計(jì)實(shí)現(xiàn)包括以太網(wǎng),USB、RS 485等常見(jiàn)的數(shù)據(jù)接口。

評(píng)論