基于FPGA與RS422的MⅢ總線轉換板的設計與實現

(2)MIII總線收發

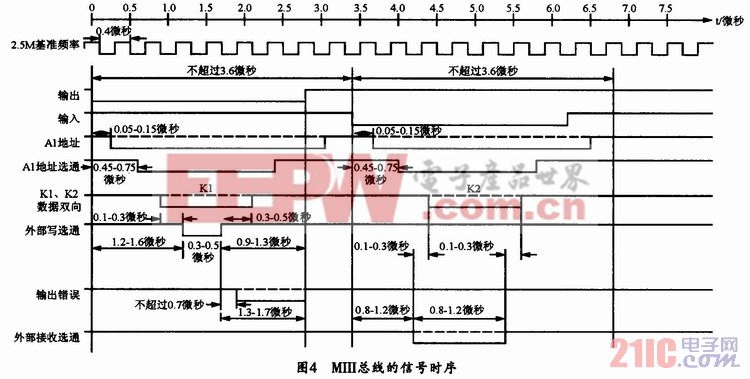

MIII總線收發功能則獨立于Nios系統。它充分利用FPGA可靈活配置的特點,并用VerilogHDL語言實現MIII總線的實時性和可靠性要求較高的關鍵部分,然后模擬MIII總線的邏輯功能,最終實現MIII總線數據、地址的收發以及與Nios系統通過自定義的接口實現通訊。MIII總線的信號時序如圖4所示。

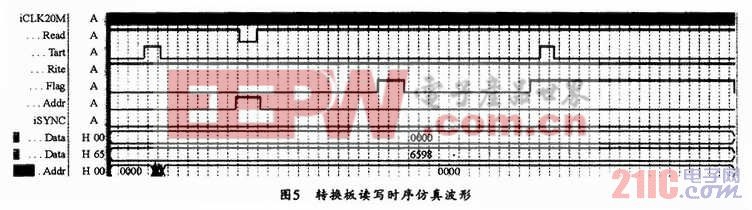

該轉換板的讀寫時序可用VerilogHDL語言描述,然后采用有限狀態機實現上述操作,并用Quartus II進行時序仿真,其仿真波形如圖5所示。

3.4 接口電平轉換電路

由于FPGA可編程器件的輸入/輸出電平通常是3.3 V,而對接MIII總線設備是OC門輸入/輸出。OC門又稱集電極開路電路,其內部電壓為+5 V。所以,FPGA的輸入/輸出需要進行兩次電壓轉換。

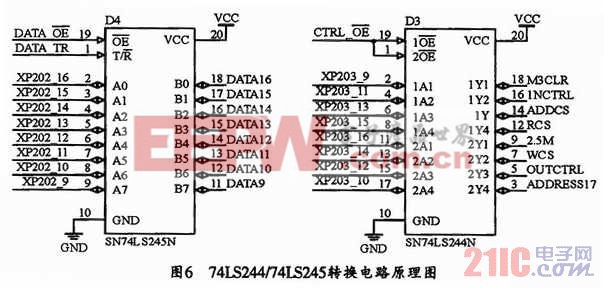

其中,第一次電壓轉換是把FPGA輸入/輸出電平的3.3 V轉換為5 V電平。由于數據信號是讀寫雙向的,而地址和控制信號是單向的(由MIII總線發送到對接MIII總線設備),因此,其數據信號應當用74LS245芯片來進行轉換,而地址和控制線則應用74LS244芯片來轉換,其電路原理如圖6所示。

由于對接MIII總線設備內部是OC門輸入/輸出,而且由于OC門電路的輸出管的集電極懸空,使用時需外接一個上拉電阻到電源。一般情況下,OC門會使用上拉電阻以輸出高電平,此外,為了加大輸出引腳的驅動能力,選擇上拉電阻阻值的原則是降低功耗及芯片的灌電流能力應當足夠大,從而確保足夠的驅動電流足夠小。其具體的電平轉換電路原理圖如圖7所示。

FPGA輸入/輸出的信號,經過以上兩個步驟的電平轉換,就能符合MIII總線對接設備的輸入/輸出信號要求。至此,只需MIII總線轉換板輸入/輸出的地址、數據和控制信號按照MIII總線時序進行收發,就可以實現MIII總線通信。

4 結束語

本文介紹了某型火控電子設備的專用數據通信總線(MIII總線)轉換板的設計方法,給出了MIII總線的總線通信功能。同時介紹了應用F-PGA實現MIII總線部分電路的實現方法。事實上,利用FPGA可簡化系統結構,縮短設計周期,提高系統的性能和可擴展性。目前,該轉換板經過與某型火控電子設備聯調證明,其功能正常,工作穩定,且已得到了用戶好評,收到了良好的社會和經濟效益。

評論