基于VHDL +FPGA 的自動售貨機控制模塊的設計與實現(xiàn)

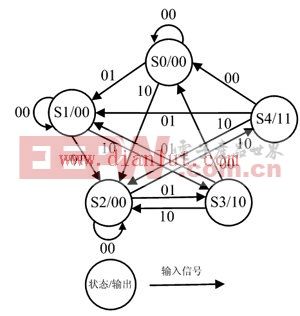

根據(jù)圖1所示的狀態(tài)轉換圖,用VHDL中的CASE_WHEN結構和IF_THEN_ELSE語句實現(xiàn)控制功能,源程序如下:

LIBRARY IEEE; --庫和程序包的使用說明

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY sellmachine IS --實體定義

PORT(clk,reset: IN std_logic;

state_inputs:IN std_logic_vector(0 TO 1);

comb_outputs:OUT std_logic_vector(0 TO 1));

END sellmachine;

ARCHITECTURE state OF sellmachine IS --結構體

TYPE fsm_st IS (S0,S1,S2,S3,S4); --狀態(tài)枚舉類型定義

SIGNAL current_state,next_state:fsm_st; --狀態(tài)信號的定義

BEGIN

reg:PROCESS(reset,clk) --時序進程

BEGIN

IF reset='1' THEN current_state=S0; --異步復位

ELSIF rising_edge(clk) THEN

current_state=next_state; --狀態(tài)轉換

END IF;

END PROCESS;

corn:PROCESS(current_state,state_inputs) --組合進程

BEGIN

CASE current_state IS

WHEN S0=>comb_outputs=00; --現(xiàn)態(tài)S0

IF state_inputs=00 THEN next_state=S0; --輸入不同,次態(tài)不同

ELSIF state_inputs=01 THEN next_state=S1;

ELSIF state_inputs=10 THEN next_state=S2;

END IF;

WHEN S1=>comb_outputs=00; --現(xiàn)態(tài)S1

IF state_inputs=00 THEN next_state=S1; --輸入不同,次態(tài)不同

ELSIF state_inputs=01 THEN next_state=S2;

ELSIF state_inputs=10 THEN next_state=S3;

END IF;

WHEN S2=>comb_outputs=00; --現(xiàn)態(tài)S2

IF state_inputs=00 THEN next_state=S2; --輸入不同,次態(tài)不同

ELSIF state_inputs=01 THEN next_state=S3;

ELSIF state_inputs=10 THEN next_state=S4;

END IF;

WHEN S3=>comb_outputs=10; --現(xiàn)態(tài)S3

IF state_inputs=00 THEN next_state=S0; --輸入不同,次態(tài)不同

ELSIF state_inputs=01 THEN next_state=S1;

ELSIF state_inputs=10 THEN next_state=S2;

END IF;

WHEN S4=>comb_outputs=11; --現(xiàn)態(tài)S4

IF state_inputs=00 THEN next_state=S0; --輸入不同,次態(tài)不同

ELSIF state_inputs=01 THEN next_state=S1;

ELSIF state_inputs=10 THEN next_state=S2;

END IF;

END CASE;

END PROCESS;

END state;

評論