基于FPGA的電子穩像系統的設計

由于系統中進行放大變換采用FPGA實現,因此本文討論的重點在于如何簡化實現并提高轉換速度,上轉換中的上采樣過程為:

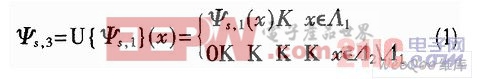

(1)式中Ψs,1和Ψs,3分別為原理圖像和上采樣信號;U(.)為上采樣運算;Λ2Λ1表示在Λ2而不在Λ1內的點的集合。插值濾波器的定義如下:

(2)式中,d(Λ)為柵格Λ的采樣密度;v*表示柵格Λ的轉逆柵格的Voronoi單元,即柵格Λ原點的單位元,它向所有柵格點平移將會無重疊地覆蓋整個連續空間。最簡單的插值濾波為線性插值,也可以采用二加權濾波的方法。圖像的縮放還可以采用3次樣條插值和小波分解的方法,雖然這些方法在理論上可以取得很好的圖像縮放效果,但計算復雜,即使采用快速算法,也難以實現視頻圖像的實時顯示。

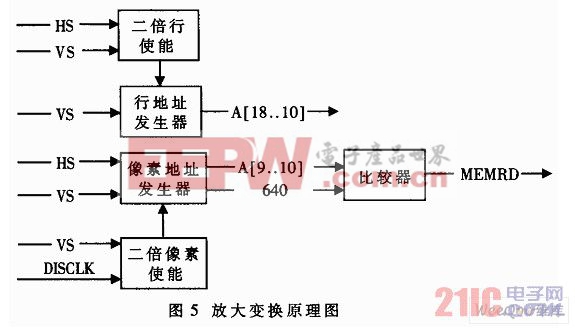

針對視頻信號數據量大、數據流速度的特點,采用FPGA設計,可以完成幀存控制、視頻信號的實時放大與疊加功能。基于運算速度與算法實現的難易程度分析,對視頻信號的放大采用了簡單的線性插值的辦法,原理如圖5所示。視頻信號是以場或幀進行存儲的,由于數據寫入時存儲地址與圖像顯示的空間位置有確定的對應關系,因此系統需要的放大處理就變為對幀存儲體的地址線的控制問題。

對于本系統具體的4倍放大要求,將行同步信號先進行二倍行使能運算,并利用場同步信號對該寄存器進行復位,將生成后的二分頻行同步信號控制行地址發生器,也就是產生幀存儲器所需的高位地址;類似地利用像素時鐘、行同步信號和場同步信號就可以得到所需的低位地址。由于在幀存控制器向幀存儲器寫入數據時采用了一行點1024個位置的辦法,所以在低位地址后連接了一個比較器,當產生的低位地址小于640時,幀存儲器的讀信號有效,否則無效,以保證不會混疊入無效的數據。

1.5 VGA接口控制器

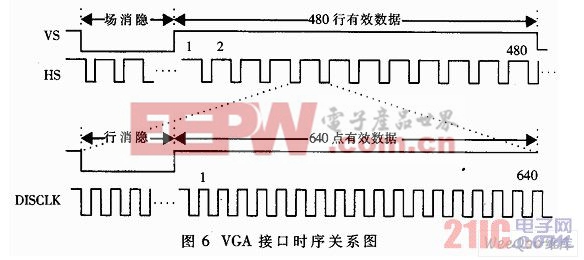

標準的VGA(640×480,60Hz)接口需要提供以下幾組信號:3個RGB模擬信號、行同步信號HS和場同步信號VS。它的信號時序如圖6所示。

圖6中VS為場同步信號,場周期為16.683ms,每場有525行,其中480行為有效顯示行,45行為場消隱區,場同步信號每場有一個脈沖,該脈沖的低電平寬度為63μs(2行)。行周期為31.78μs,每顯示行包括800點,其中640點為有效顯示區,160點為行消隱區(非顯示區)。行同步信號HS每行有一個脈沖。該脈沖的低電平寬度為3.81μs(即96個脈沖)。因此,VGA控制器的任務就是按要求產生所需要的時序。

評論