基于電磁兼容技術的多層PCB布線設計

(1)確定哪個參考平面層將包含用于不同的DC電壓的多個電源區. 假設第11層有多個DC電壓,就意味著設計者必須將高速信號盡可能遠離第10層和底層,因為返回電流不能流過第10層以上的參考平面,并且需要使用縫合電容,第3、5、7和9層分別為高速信號的信號層. 重要信號的走線盡可能以一個方向布局,以便優化層上可能的走線通道數. 分布在不同層上的信號走線應互相垂直,這樣可以減少線間的電場和磁場的耦合干擾,第3和第7層可以設定為“東西”走線,而第5和第9層設置為“南北”走線. 走線布在哪一層要根據其到達目的地的方向.

(2)高速信號走線時層的變化,及哪些不同的層用于一個獨立的走線,確保返回電流從一個參考平面流到需要的新參考平面. 這樣是為了減小信號環路面積,減小環路的差模電流輻射和共模電流輻射. 環路輻射與電流強度、環路面積成正比. 實際上,最好的設計并不要求返回電流改變參考平面,而是簡單地從參考平面的一側改變到另一側. 如信號層的組合可以用作信號層對:第3層和第5層,第5層和第7層,第7層和第9層,這就允許一個東西方向和南北方向形成一個布線組合. 但是第3層和第9層的組合就不應使用,因為這要求返回電流從第4層流到第8層. 盡管一個去耦電容可以放置在過孔附近,但在高頻時由于存在引線和過孔電感而使電容失去作用. 并且這種走線會使信號環路面積增大,不利減小電流輻射.

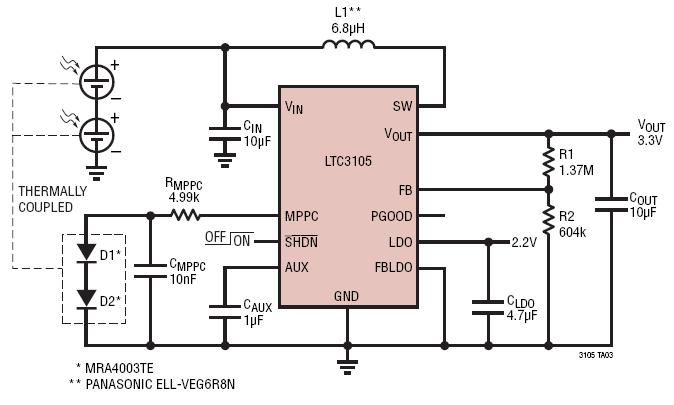

(3)為參考平面層選定DC電壓. 該例中,由于處理器內部信號處理的高速性,致使在電源/地參考引腳上存在大量的噪聲. 因此,在為處理器提供相同DC電壓上使用去耦電容器非常重要,并且盡可能有效地使用去耦電容器. 降低這些元件電感的最好方法是連接走線盡可能短和寬,并且盡可能使過孔短和粗.

如果第2層分配為“地”,且第4層分配為處理器的電源,則過孔距離放置處理器和去耦電容器的頂層應該盡可能短. 延伸到板的底層的過空剩余部分不包含任何重要的電流,而且距離短不會具有天線作用. 表1列出了疊層設計布局的參考配置.

2. 2 20 - H規則及3 -W 法則

在多層PCB板電磁兼容性設計中,確定多層板電源層與邊沿的距離和解決印制條間的距離有兩個基本原則: 20 - H規則及3 - W法則 .

評論