基于FPGA的星載計(jì)算機(jī)自檢EDAC電路設(shè)計(jì)

從圖中可以看出,啟動(dòng)EDAC自檢后,EDAC開(kāi)始巡檢RAM存儲(chǔ)單元,產(chǎn)生錯(cuò)誤中斷(標(biāo)志) 信號(hào),給出錯(cuò)誤信息。當(dāng)單片機(jī)需要處理中斷時(shí),將Check信號(hào)置‘0’,可暫時(shí)停止巡檢, 此時(shí)單片機(jī)可對(duì)RAM存儲(chǔ)單元進(jìn)行正常讀寫(xiě)操作。等中斷處理完后,單片機(jī)將Check信號(hào)置 ‘1’,恢復(fù)RAM巡檢操作。

另外可通過(guò)Rw_En的置‘0’或‘1’,來(lái)控制禁止或允許進(jìn)行自糾錯(cuò)操作。

當(dāng)出現(xiàn)可識(shí)別的多位錯(cuò)誤時(shí),產(chǎn)生Err和MErr兩個(gè)錯(cuò)誤中斷(標(biāo)志)信號(hào),但由于漢明碼僅能糾正單比特錯(cuò)誤,因此不進(jìn)行自糾錯(cuò)操作。

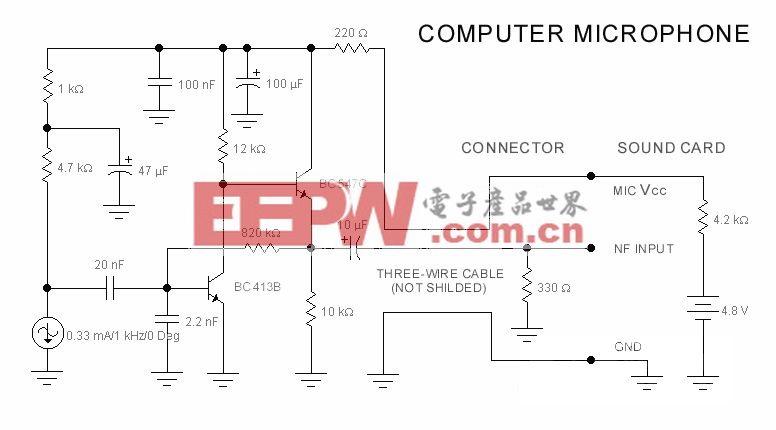

從原注入錯(cuò)誤數(shù)據(jù)對(duì)應(yīng)的地址讀出數(shù)據(jù),仿真輸出結(jié)果如圖4所示。

可以看出除最后一個(gè)地址(FFH)由于兩位錯(cuò)仍輸出錯(cuò)誤外,其他地址輸出數(shù)據(jù)均與地址相同,即為正確數(shù)據(jù)。

其中,24H、3CH、60H三個(gè)地址雖然輸出正確數(shù)據(jù),但仍報(bào)錯(cuò),表明存儲(chǔ)器內(nèi)數(shù)據(jù)仍然 為錯(cuò)誤數(shù)據(jù),在輸出時(shí)進(jìn)行了糾錯(cuò)。這是由于在上次巡檢到這部分地址空間時(shí),通過(guò)把Rw_En 信號(hào)拉低,從而禁止了自動(dòng)糾錯(cuò),導(dǎo)致這三個(gè)地址錯(cuò)誤數(shù)據(jù)未被糾正。而在對(duì)其他地址進(jìn)行 數(shù)據(jù)讀取時(shí),未產(chǎn)生錯(cuò)誤標(biāo)志,證明其他錯(cuò)誤數(shù)據(jù)已被糾錯(cuò)。

4 結(jié)論

本文在采用FPGA芯片實(shí)現(xiàn)基本EDAC讀寫(xiě)功能的設(shè)計(jì)思路基礎(chǔ)上,創(chuàng)建了一種新型的可對(duì) RAM存儲(chǔ)單元進(jìn)行自檢的EDAC功能模塊。該模塊不但可以對(duì)RAM存儲(chǔ)單元進(jìn)行快速巡檢,巡檢 時(shí)間僅為傳統(tǒng)EDAC方法的十二分之一,還可以自動(dòng)糾正已發(fā)現(xiàn)的錯(cuò)誤。該模塊最大的優(yōu)點(diǎn)在 于節(jié)省了單片機(jī)資源,幾乎不需要單片機(jī)的參與即可完成所有自檢功能,從而使基于FPGA 的星載計(jì)算機(jī)對(duì)SEU事件防護(hù)能力得到較大的提升。本文中該模塊采用Verilog硬件描述語(yǔ)言 編程,具有可移植性,這種設(shè)計(jì)方法可用于各種體系結(jié)構(gòu)的星載計(jì)算機(jī)中。

本文作者創(chuàng)新點(diǎn): 通過(guò)引入FPGA技術(shù),設(shè)計(jì)了一種靈活、高效的自檢EDAC電路,可在CPU 的控制下實(shí)現(xiàn)對(duì)錯(cuò)誤信息的自動(dòng)處理,并提出了該EDAC電路驗(yàn)證方法。

評(píng)論