基于FPGA的單片機外圍接口電路設計

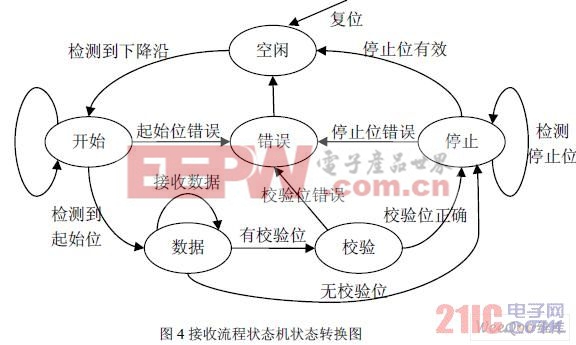

2.4.1 接收模塊

異步串行通信是逐個字符進行傳輸的,并且傳送的每一個字符格式都相同,均以一位起始位開始,中間有若干位數據位,然后是一位校驗位(可選),昀后是停止位,停止位后面是不定長度的空閑位。這樣就保證了起始位開始處一定有一個下跳沿。接收邏輯首先通過檢測數據的下降沿來檢測起始位,產生采樣時鐘,然后利用采樣時鐘來采樣串行輸入數據,在緩沖器中做移位操作,同時產生校驗位,在第 8位處比較校驗位是否正確,在第 9位處比較停止位是否為高,然后產生錯誤指示信號。本文采用狀態機進行設計,其 FSM狀態轉換圖如圖 4所示。

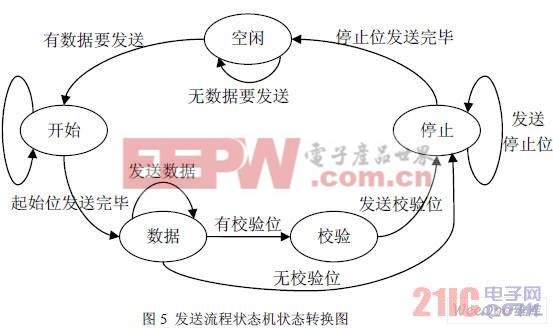

2.4.2 發送模塊

發送部分檢測控制信號,當有數據要發送時只要按順序依次發送 1位起始位、 5-7位數據位、一位校驗位(帶校驗時)和 1位(或 1.5位、2位)停止位即可。其 FSM狀態轉換圖如圖 5所示。

停止位發送完畢

無數據要發送發送停止位

3 結束語

將設計下載到芯片中,綜合報告顯示只消耗了FPGA很少的一部分資源。整個系統的功耗也大為降低。由于FPGA為大規模集成電路,其集成度和工作速度隨著技術進步和產品升級不斷提高,所以用FPGA實現單片機外圍接口電路可以大大改善單片機系統的性能,系統的外圍邏輯越是復雜,FPGA的潛力越能得到更好的發揮。

評論