基于FPGA的慣導系統溫控電路接口設計

4 FPGA 與外圍電路之間的通信接口

FPGA 與外圍電路之間的通信接口主要包括與溫度傳感器,DSP,232 接口芯片和DAC的通信接口四個部分。

(1) 與溫度傳感器的通信接口

本方案的溫度傳感器采用DS18B20,它通過硬件非常簡單的1-wire 總線通信,由于硬件簡單所以通信協議比較復雜。要實現與它的通信接口將占用大量FPGA 片內資源,而且本方案要進行七路溫度采集,因此優化程序設計,減少冗余,節省資源顯得尤為重要。

(2) 與DSP 的通信接口

DSP 與FPGA 的組合已經成為當今數字電路中非常流行的模式。FPGA 非常適合與DSP配合。本方案中,DSP 與FPGA 的通信接口主要由數據總線,地址總線和一些控制信號組成。FPGA 和DSP 之間由8 位數據總線連接,數據以字節形式并行傳輸。DSP 通過地址總線對FPGA的片內資源尋址。控制信號主要包括復位信號,中斷信號和讀寫信號。

(3) 與232 接口芯片的通信接口

FPGA 與232 接口芯片的通信是通過收發兩條數據線實現的。本方案中,只存在溫控系統到上位機的單向數據傳輸,故僅需一條發送數據線就可以完成與232 接口芯片的通信。

(4) 與DAC 的通信接口

本方案選用TI 公司的TLV5620I 芯片作為DAC。它是8 位4 路電壓數模轉換器。對于它的數字控制基于由4 條信號線組成的串行總線。包括CLK,DATA,LOAD 和LDAC 四種信號。

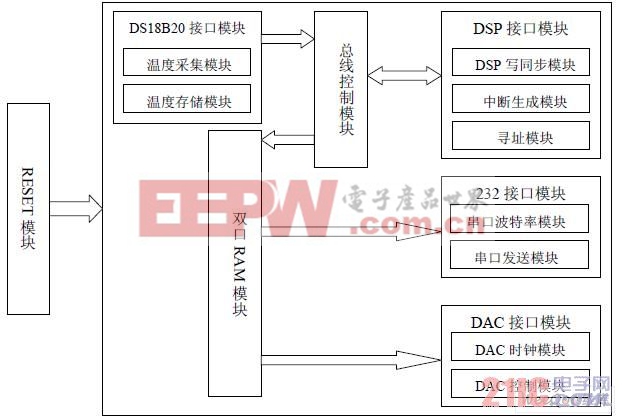

5 FPGA 的邏輯設計

在溫控電路的總體方案,硬件結構,工作流程和接口協議都確定后,就可以進行FPGA的邏輯設計了。FPGA 的邏輯設計是整個溫控電路接口設計的重中之重。它基于verilog 硬件描述語言。良好的FPGA 邏輯設計應該是時序清晰,運行穩定,結果明確和節省資源的。它能夠保證整個系統的可靠,穩定和高效。FPGA 的邏輯模塊圖如圖3 所示。FPGA 內部邏輯大致分為RESET 模塊,DS18B20 接口模塊,總線控制模塊,DSP 接口模塊,雙口RAM 模塊,232 接口模塊和DAC 接口模塊等幾部分。

圖3 FPGA 的邏輯模塊圖

(1)RESET 模塊

該模塊生成全局復位信號。是所有模塊中優先級最高的。系統上電后,該模塊將復位信號拉低并持續1 秒而后拉高,對DSP 和FPGA 內部其他模塊進行復位。

(2)DS18B20 接口模塊

該模塊用于實現與DS18B20 通信,讀取并存儲溫度值。它包含2 個子模塊。

一、溫度采集模塊

該模塊實現與DS18B20 的通信協議。首先通過一個初始化序列對DS18B20 進行初始化,包括一個由主機發出的復位脈沖和其后由從機發出的存在脈沖。探測到存在脈沖之后,代表初始化完成,模塊將發送ROM 操作命令。本方案中,執行SKIP ROM 跳過ROM 匹配。之后將發送存儲器操作命令。溫度轉化和讀取溫度就在這部分完成。其中每一次讀寫操作都需要嚴格按照DS18B20 的讀寫時隙進行。該模塊復雜程度高和占用資源多,是整個FPGA 中的重要模塊。本方案一共有七路溫度采集模塊,它們的并行結構使得系統可以方便地實現對七路溫度的實時監控。

二、溫度存儲模塊

該模塊的主要構成部分是一個14*8 位存儲器,用于存儲七路溫度數值,每一路數值需要2 個8 位寄存器存放。存儲完畢后,等待DSP 讀取。

(3)DSP 接口模塊

該模塊主要用于與DSP 進行通信。它包含3 個子模塊。

評論