LabVIEW FPGA和軟件設(shè)計射頻儀器簡介

概覽

本文引用地址:http://www.104case.com/article/189890.htm無線設(shè)備的數(shù)量、通信標(biāo)準(zhǔn)的多樣性,以及調(diào)制方案的復(fù)雜度,每一年都在不斷增加。而隨著每一代新技術(shù)的誕生,由于使用傳統(tǒng)技術(shù)測試無線設(shè)備,需要大量更復(fù)雜的測試設(shè)備,其成本也在不斷提高。

使用虛擬(軟件)儀器與模塊化I/O相結(jié)合是一種最小化硬件成本并減少測試時間的方法。軟件設(shè)計儀器的新方法使得射頻測試工程師無需憑借自定義或特殊標(biāo)準(zhǔn)的儀器,就能以多個數(shù)量級的幅度減少測試時間。

閱讀此文可以幫助您了解如何使用NI LabVIEW FPGA來設(shè)計和自定義您的射頻儀器,以及通過軟件設(shè)計的儀器能為您的測試系統(tǒng)所帶來的好處。

軟件設(shè)計儀器簡介

多年來,測試工程師一直在運用諸如LabVIEW的軟件包來實現(xiàn)自定義射頻測量系統(tǒng),并與傳統(tǒng)封裝儀器相比盡可能地減少成本。使用軟件設(shè)計的方法不僅提供了強大的靈活性,更能使測試工程師利用到最新的PC,CPU和總線技術(shù)所帶來的性能提升。

CPU成為了許多高要求射頻測試應(yīng)用的瓶頸,CPU有限的并行機制和軟件棧將會導(dǎo)致延時,對于有些需要根據(jù)測量值或待測設(shè)備(DUT)的狀態(tài)而動態(tài)調(diào)整測試激勵的應(yīng)用,就會影響到測試效果。為了達到最理想的射頻測試系統(tǒng)效果,需要結(jié)合使用自定義儀器硬件和多核技術(shù),這也能使測試系統(tǒng)設(shè)計人員得以找到低延時和高吞吐量之間的平衡點,從而大幅減少測試時間。

雖然現(xiàn)成即用的儀器硬件的性能早已被改善,NI仍然致力于運用現(xiàn)場可編程門陣列(FPGA)技術(shù)提供更加開放和靈活的測試設(shè)備。簡而言之,FPGA是一種用戶可以自定義的高密度的數(shù)字芯片,可以使得測試工程師將他們的自定義信號處理方法和控制算法結(jié)合到測試硬件中。因此,即成可用的射頻硬件包含了諸多優(yōu)點:高質(zhì)量的測量技術(shù),且在其最新的構(gòu)件中包含了可靠的,可溯源的測量方法,通過與高度并行的用戶自定義邏輯相結(jié)合,可以產(chǎn)生較低的延遲,并且它能夠與I/O直接連接以用于在線處理和嚴格的控制環(huán)路。

關(guān)于此類硬件的一個案例是NI PXIe-5644R vector signal transceiver (VST)。該設(shè)備融合了矢量信號發(fā)生器和矢量信號分析儀的功能,并包含了一個用戶可編程FPGA來用于實時信號處理和控制。由于FPGA賦予其更多的靈活性,VST非常適合用于自定義觸發(fā),待測設(shè)備控制,并行測試和實時數(shù)字信號處理(DSP)。

使用LabVIEW FPGA將LabVIEW的運用擴展至硬件自定義

雖然FPGA已廣泛用于自定義主板設(shè)計或是即成可用設(shè)備的一部分,但用戶自定義FPGA迄今為止還未被大量用于即成可用的射頻儀器設(shè)備中。這主要是因為對這些設(shè)備進行編程需要擁有專業(yè)的背景知識。硬件描述語言或HDL,通常學(xué)習(xí)起來非常困難,唯有數(shù)字電路設(shè)計專家才能勝任。

LabVIEW FPGA模塊可以幫助大量的工程師和科學(xué)家接觸到最新的FPGA技術(shù)。使用圖形化編程方法,用戶可以在硬件中實現(xiàn)邏輯定義射頻儀器的行為。事實上,LabVIEW的圖形化數(shù)據(jù)流的特性非常適合用于實現(xiàn)并視覺化呈現(xiàn)那些可在FPGA上進行的并行操作。雖然使用LabVIEW對FPGA編程還是略有區(qū)別,也需要進行額外的學(xué)習(xí),但其難度將明顯小于學(xué)習(xí)HDL的難度。

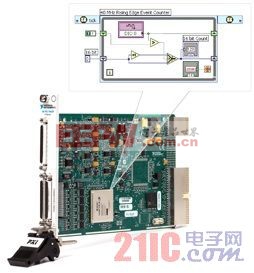

圖1,使用LabVIEW FPGA模塊,用戶可以使用熟悉的LabVIEW代碼對儀器硬件進行自定義。對于射頻應(yīng)用,用戶可以以預(yù)創(chuàng)建的范例項目為基礎(chǔ),添加相應(yīng)修改以實現(xiàn)自定義觸發(fā),待測設(shè)備控制,信號處理等功能。

許多LabVIEW FPGA的范例項目都可以作為您射頻應(yīng)用的起始點,并且這些項目也能在諸如NI PXIe-5644R VST之類的設(shè)備上使用。值得一提的是,用戶可以根據(jù)儀器數(shù)據(jù)移動模式(與矢量信號分析儀或發(fā)生器擁有相似的自定義開始,停止和參考觸發(fā)顯示界面),或者根據(jù)數(shù)據(jù)流模式(適用于在線信號處理或者錄制和回放應(yīng)用)對FPGA進行自定義。

軟件設(shè)計儀器與傳統(tǒng)方法的對比

在射頻測量系統(tǒng)中運用基于FPGA的硬件可以帶來從低延時待測設(shè)備的控制到減少CPU負載等諸多好處。在下文中將介紹更多不同應(yīng)用的詳細情況。

使用交互式待測設(shè)備控制方法,提高測試系統(tǒng)的整合度

在許多射頻測試系統(tǒng)中,需要使用數(shù)字信號或自定義協(xié)議來控制需要被控制的設(shè)備和芯片。傳統(tǒng)的自動化測試系統(tǒng)可以通過待測設(shè)備的模式進行排序,在每一個不同的階段進行所需的測量工作。有些智能型的自動化測試儀器(ATE)系統(tǒng)可以根據(jù)接收到的測量值在待測設(shè)備設(shè)置之間進行排序。

對于任意兩種情況,包含了FPGA的軟件設(shè)計儀器都可以降低成本并減少測試時間。將測量處理和數(shù)字控制整合至一個儀器中可以降低系統(tǒng)對其他數(shù)字I/O的需求,并且也無需在儀器間對觸發(fā)進行配置。對于有些必須根據(jù)接受到的測量數(shù)據(jù)進行控制的待測設(shè)備,軟件設(shè)計儀器可以在硬件中關(guān)閉循環(huán),以減少因在軟件中進行決策所帶來的高延時。

評論