利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口

低成本存儲器接口

今天,并不是所有的系統都在追求存儲器接口的性能極限。當低成本是主要的決定因素,而且存儲器的比特率達到每引腳 333 Mb/s 已經足夠時,Spartan-3 系列 FPGA配之以 Xilinx 軟件工具,就能提供一個易于實現、低成本的解決方案。

基于 FPGA 設計的存儲器接口和控制器由三個基本構建模塊組成:讀寫數據接口、存儲器控制器狀態機,以及將存儲器接口設計橋接到 FPGA 設計的其余部分的用戶界面(圖3)。這些模塊都在 FPGA 資源中實現,并由數字時鐘管理器 (DCM) 的輸出作為時鐘來驅動。在 Spartan-3 系列實現中,DCM 也驅動查找表 (LUT) 延遲校準監視器(一個確保讀數據采集具有正確時序的邏輯塊)。延遲校準電路用來選擇基于 LUT 的延遲單元的數量,這些延遲單元則用于針對讀數據對選通脈沖線 (DQS) 加以延遲。延遲校準電路計算出與 DQS 延遲電路相同的一個電路的延遲。校準時會考慮所有延遲因素,包括所有組件和布線延遲。

用戶界面是一種握手型的界面。用戶發出一條讀或寫命令,如果是寫命令的話還包括地址和數據,而用戶界面邏輯以 User_cmd-ack 信號回應,于是下一條命令又可發出。

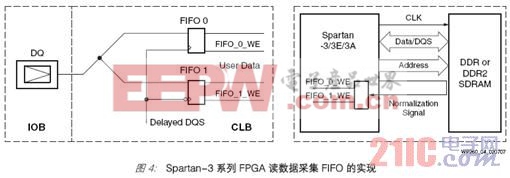

在 Spartan-3 系列實現中,使用可配置邏輯塊 (CLB) 中的 LUT 來實現讀數據采集。在讀事務過程中,DDR 或 DDR2 SDRAM 器件將讀數據選通脈沖 (DQS) 及相關數據按照與讀數據 (DQ) 邊沿對齊的方式發送給 FPGA。在高頻率運行的源同步接口中采集讀數據是一項頗具挑戰性的任務, 因為數據在非自由運行 DQS 的每個邊沿上都會改變。讀數據采集的實現使用了一種基于 LUT 的 tap 延遲機制。DQS 時鐘信號被適量延遲,使其放置后在讀數據有效窗口中具有足夠的余量,以在 FPGA 內被采集。

讀數據的采集是在基于 LUT 的雙端口分布式 RAM 中完成的(見圖4)。LUT RAM 被配置成一對 FIFO,每個數據位都被輸入到上升邊沿 (FIFO 0) 和下降邊沿 (FIFO 1)的FIFO 中,如圖4 所示。這些深度為 16 個輸入的 FIFO 異步運行,具有獨立的讀寫端口。

來自存儲器的讀數據寫到經過延遲的 DQS 上升邊沿的 FIFO_0 中,并寫到經過延遲的DQS 下降邊沿的 FIFO_1 中。將讀數據從 DQS 時鐘域傳輸到存儲器控制器時鐘域就是通過這些異步 FIFO 完成的。在存儲器控制器的時鐘域中,可以從 FIFO_0 和FIFO_1 同時讀出數據。FIFO 的讀指針在 FPGA 的內部時鐘域中生成。寫使能信號(FIFO_0 WE 和 FIFO1_WE)的生成通過 DQS 和一個外部回送(亦即歸一化)信號完成。外部歸一化信號作為輸出傳送至輸入/ 輸出模塊 (IOB),然后通過輸入緩沖器作為輸入取出。這種技術可補償 FPGA 與存儲器器件之間的 IOB、器件和跡線延遲。從FPGA 輸入管腳發出的歸一化信號在進入 LUT 延遲電路之前使用與 DQS 相似的布線

資源,以與布線延遲相匹配。環路之跡線延遲應為發送給存儲器的時鐘和 DQS 之跡線

延遲的總和(圖4)。

寫數據命令和時序由寫數據接口生成并控制。寫數據接口使用 IOB 觸發器和 DCM 的90 度、180 度和 270 度輸出,發送按照 DDR 和 DDR2 SDRAM 的時序要求與命令位和數據位正確對齊的 DQS。

用于 Spartan-3 系列 FPGA 的一種 DDR 和 DDR2 SDRAM 存儲器接口實現已通過硬件進行了充分驗證。一個利用 Spartan-3A 入門套件的低成本 DDR2 SDRAM 參考設計示例已完成。此設計為板上 16 位寬 DDR2SDRAM 存儲器器件而開發,并使用了XC3S700A-FG484。此參考設計僅利用了 Spartan-3A FPGA 器件可用資源的一小部分:13% 的 IOB、9% 的邏輯 Slice、16% 的 BUFG MUX 和八個 DCM 中的一個。這一實現為其余部分 FPGA 設計所需的其他功能留下了可用資源。

使用存儲器接口生成器 (MIG) 軟件工具(本白皮書后面的部分有說明),設計人員可以很容易地定制 Spartan-3 系列的存儲器接口設計,以適合自己的應用。

高性能存儲器接口

隨著數據速率的提高,滿足接口時序方面的要求變得愈益困難了。與寫入存儲器相比,從存儲器中讀數據時,存儲器接口時鐘控制方面的要求通常更難滿足。追求更高數據速率的趨勢使得設計人員面臨巨大挑戰,因為數據有效窗口(此為數據周期內的一段時間,其間可獲得可靠的讀數據)比數據周期本身縮小得快。造成這種情況的原因是,影響有效數據窗口尺寸大小的系統和器件性能參數具有種種不確定性,它們縮小的速率與數據周期不同。

如果比較一下運行速度為 400 Mb/s 的 DDR SDRAM 數據有效窗口和運行速度為 667

Mb/s 的 DDR2 存儲器技術,這種情況就一目了然了。數據周期為 2.5 ns 的 DDR 器件擁有 0.7 ns 的數據有效窗口,而數據周期為 1.5 ns 的 DDR2 器件僅有 0.14 ns 的數據有效窗口(圖5)。

顯然,數據有效窗口的加速減損給 FPGA 設計人員帶來了一堆全新的設計挑戰,要創建和維護可靠的存儲器接口性能,就得采用更有效的方法。

評論