基于FPGA實現(xiàn)的計算機與HDTV顯示器測試信號發(fā)生器

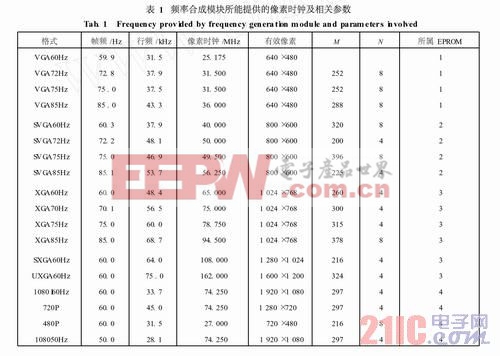

需要說明的是,MC12429與MC10ELT21組成的頻率合成系統(tǒng)無法產(chǎn)生25.175MHz(VGA60Hz)的時鐘頻率,因而還需要外加一個25.175MHz的晶體振蕩器為VGA60顯示格式提供時鐘.此外,THS8134的最大輸入頻率是80MHz,所以對像素時鐘大于80MHz的顯示格式(XGA85Hz、SXGA60Hz和UXGA602Hz),采取FPGA片外分頻的方法,即讓時鐘合成模塊輸出像素時鐘的2分頻,從而使THS8134的輸入時鐘都小于80MHz.這樣做的代價是,系統(tǒng)水平方向以2個像素為單位進(jìn)行處理.該模塊如圖2所示.表1給出了本儀器可以測試的格式及相關(guān)參數(shù).

圖2 頻率產(chǎn)生框圖

表1 頻率合成模塊所能提供的像素時鐘及相關(guān)參數(shù)

3 FPGA程序設(shè)計

本儀器性能上的改進(jìn)主要是通過對FPGA重新編程實現(xiàn)的.在設(shè)計過程中使用了MAX+PLUSⅡ軟件以及AHDL語言.

1)時鐘模塊

根據(jù)選擇信號輸出相應(yīng)的像素時鐘選擇信號,并對輸入時鐘進(jìn)行分頻.由于本儀器所需要的像素時鐘大多超過了FPGA可穩(wěn)定工作的范圍,所以必須對輸入的時鐘進(jìn)行分頻.如果對時鐘進(jìn)行N分頻,那么FPGA水平方向便以N個像素為單位進(jìn)行處理,其代價是測試圖像的垂直條紋變粗(為以前的N倍),因此要適當(dāng)選擇分頻倍數(shù),使顯示效果達(dá)到芯片所允許的最佳狀態(tài).時鐘模塊還要輸出一路未分頻的時鐘信號,用于D/A變換.

2)像素計數(shù)模塊

該模塊是整個FPGA工作的基礎(chǔ).根據(jù)當(dāng)前格式下每行的像素數(shù),對像素時鐘進(jìn)行計數(shù).計數(shù)器完成1行的計數(shù)后清零并產(chǎn)生完成1行的標(biāo)志信號.

3)行計數(shù)模塊

計數(shù)器根據(jù)當(dāng)前格式下每場/幀的行數(shù),對像素計數(shù)模塊產(chǎn)生的標(biāo)志信號進(jìn)行計數(shù),再根據(jù)像素計數(shù)器和行計數(shù)器的值,在相應(yīng)的像素位置產(chǎn)生VGA輸出所需要的同步信號.完成1場/幀的計數(shù)后,計數(shù)器清零并產(chǎn)生完成一場/幀的標(biāo)志信號.

4)行控制模塊

輸出行標(biāo)志信號,使FPGA適應(yīng)不同格式的圖像輸出,不同格式是指消隱與有效輸出之間比例關(guān)系的不同.該模塊利用行計數(shù)的結(jié)果對行進(jìn)行分類,并將行類型碼傳給同步/消隱控制信號產(chǎn)生模塊.

5)同步/消隱控制信號產(chǎn)生模塊

根據(jù)像素計數(shù)器的計數(shù)和行控制模塊輸出的行標(biāo)志信號,產(chǎn)生THS8134要用到的同步/消隱控制信號/SYNC、SYNC-T和/BLANK.

評論