基于FPGA的等精度頻率計的設計與實現

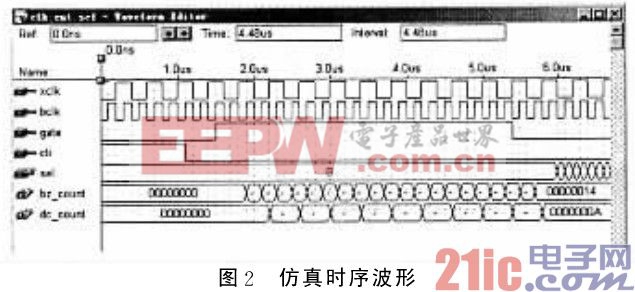

仿真波形如圖2所示。

3 結 語

本文利用ALTERA公司的FPGA芯片EPF10K10,使用VHDL編程語言設計等精度頻率計,給出核心程序,經過ISPEXPER仿真后,驗證設計是成功的,達到預期結果。

和傳統的頻率計相比,FPGA的頻率計簡化了電路板的設計,提高了系統設計的實現性和可靠性,測頻范圍達到100 MHz,實現了數字系統硬件的軟件化,這是數字邏輯設計的新趨勢。

參考文獻

[1]李景華,杜玉遠.可編程邏輯器件與EDA技術[M].沈陽:東北大學出版社,2002.

[2]趙雅興.FPGA原理、設計與應用[M].天津:天津大學出版社,1999.

[3]夏宇聞.復雜數字電路與系統的VERILOGHDL設計技術[M].北京:北京航空航天大學出版社,1998.

評論