基于FPGA的多功能頻率計的設計

摘要:基于Altera公司FPGA芯片EP2C8Q208,嵌入MC8051 IP Core,用C語言對MC8051 IP Core進行編程,以其作為控制核心,實現系統控制。在FPGA芯片中,利用Verilog HDL語言進行編程,設計了以MC8051 IP Core為核心的控制模塊、計數模塊、鎖存模塊和LCD顯示模塊等幾部分,實現了頻率的自動測量,測量范圍為0.1Hz~50MHz,測量誤差0.01%。并實現測頻率、周期、占空比等功能。

關鍵詞:FPGA;IP Core;等精度測頻;LCD;VHD

頻率是電信號中重要的物理量,在電子、通信系統中,信號的頻率穩定度決定了整個系統的性能,準確測量信號的頻率是系統設計的重要內容。

單片機廣泛地應用于電子系統設計,其性價比高,大量的外圍接口電路,使基于單片機的電子系統設計方便,周期縮短。然而,單片機的串行工作特點決定了它的低速性和程序跑飛,另外還存在抗干擾能力不強等缺點。EDA(Electronic Design Automation)技術以計算機為工具,在Quartus II軟件平臺上,對以硬件描述語言Verilog HDL/VHDL為系統邏輯描述手段完成的設計文件,自動地完成邏輯編譯、化簡、綜合及優化、邏輯仿真,直至對特定目標芯片的適配、編譯、邏輯映射和編程下載等工作,FPGA是純硬件結構,具有較強的抗干擾能力。

文中在FPGA芯片中嵌入MC8051 IP Core,作為控制核心,利用Verilog HDL語言進行編程,設計了以MC8051 IPCore為核心的控制模塊、計數模塊、鎖存模塊和LCD顯示模塊等模塊電路,采用等精度測量法,實現了頻率的自動測量,測量范圍為0.1 Hz~50 MHz,測量誤差小于0.01%。

1 8051IP(Intelligent Property)軟核

8051單片機是以由VQM原碼(Verilog Quartus Mapping File)表達的,在QuartusII環境下能與VHDL、Verilog HDL等其他硬件描述語言混合編譯綜合,并在單片FPGA中實現全部硬件系統。

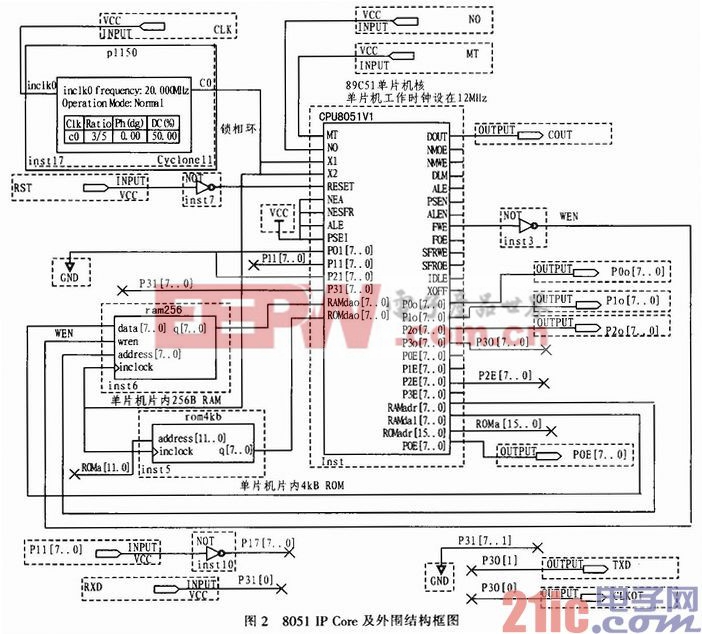

MC8051單片機核含有8位復雜指令CPU,存儲器采用哈佛結構,其結構框圖如圖1所示。

MC8051的指令系統與8051/2、8031/2等完全兼容,硬件部分也基本相同,例如可接64KB外部存儲器,可接256字節內部數據RAM,含兩個16位定時/計數器,全雙工串口,含節省功耗工作模式,中斷響應結構等。不同之處主要有:

1)MC8051是以網表文件的方式存在的,只有通過編譯綜合,并載入FPGA中才以硬件的方式工作,而普通8051總是以硬件方式存在的;

2)MC8051無內部ROM和RAM,所有程序ROM和內部RAM都必須外接。

3)以軟核方式存在能進行硬件修改和編輯;能對其進行仿真和嵌入式邏輯分析儀實現實時時序測試;能根據設計者的意愿將CPU、RAM、ROM、硬件功能模塊和接口模塊等實現于同一片FPGA中(即SOC)。

4)與普通8051不同,MC8051的4個I/O口是分開的。

MC8051核在接上了ROM和RAM后就成為一個完整的8051或8052單片機了,MC8051核實用系統的最基本構建頂層原理圖如圖2所示,主要由4個部件構成。

評論