基于FPGA的IIR數字濾波器的快捷設計

3.2 VHDL代碼頂層模塊

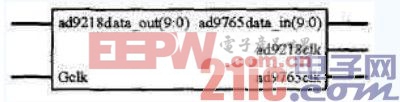

圖4是該MATLAB設計的頂層模塊“top_lev-el”的示意圖。圖中,Gclk為FPGA全局時鐘輸入(來自40MHz晶振),AD9218clk和AD9765clk是由Gclk直通送往AD9218和AD9765的驅動時鐘;AD9218data_out(9:0)是來自AD9218的10位濾波器輸入信號,設計時可與核心模塊“lpf”的輸人data_in(9:0)相連;AD9765data_in(9:0)是送往AD9765的10位濾波器輸出信號,可與核心模塊“lpf”的輸出data_out(9:0)相連。

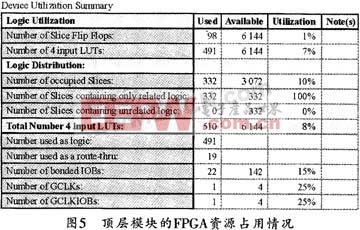

圖5給出了頂層模塊的FPGA資源占用情況,由圖5可見,該系統的資源占用率非常少。

3.3 VHDL代碼核心模塊

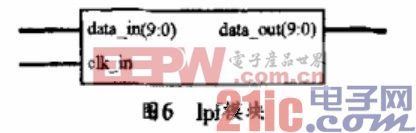

圖6所示為用于信號處理的核心模塊“lpf”。

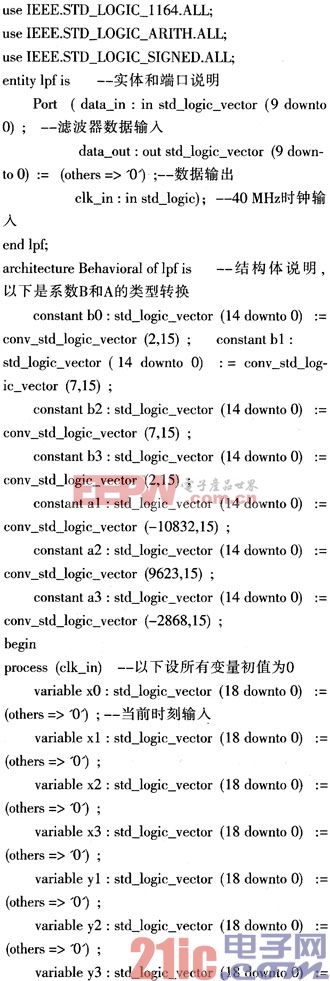

在核心模塊VHDL代碼編寫時應當注意語句“use IEEE.STD_LOGIC_SIGNED.ALL;”,并使用有符號數運算程序包。另外,在將設計好的整數系數B和A轉換為二進制補碼時,為方便起見,可使用程序包STD_LOGlC_SIGNED.vhd中的類型轉換運算符CONV_STD_LOGIC_VECTOR()來接收整數和轉換后的長度等兩個參數,然后返回STD_LOGIC_VECTOR型。

本系統的代碼結構體architecture采用行為描述方式,它類似于高級語言,其優點在于只需描述清楚輸入與輸出的行為,而無需花費更多的時間和精力關注設計功能的門級實現,因為這些完全可以由EDA工具綜合生成,因而可大大縮短開發設計的時間。

核心模塊“lpf”的VHDL語言源代碼如下:

librarv IEEE;

在modelsim上對本核心模塊進行仿真及代碼優化時,其測試激勵仍然可以分別選用0.5 MHz、3 MHz和6 MHz的正弦波。產生的方法有兩種:一是采用ISE中集成的測試激勵生成器HDL Bencher新建Test bench waveform型文件,并從中輸入一周期正弦數據;二是將正弦數據存為文本文件,然后以TEXTIO方式讀取。限于篇幅,具體操作這里不作介紹。

這種行為仿真(Simulate Behavioral Model)的波形與圖3相同,可見,本模塊源代碼在功能上完全正確。但時序仿真(布局布線后仿真SimulatePost-PlaceRoute VHDL Model)的濾波器輸出波形中的大幅度尖銳毛刺嚴重影響了濾波器的性能。消除毛刺的具體做法是將進程中的最后一條信號賦值語句改為:

經過上述賦值語句的修改,再經優化之后進行時序仿真以及后面的硬件驗證,就會發現,濾波器輸出中的毛刺全部被消除,波形平滑,可見優化效果非常好。

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

評論