短波擴頻猝發通信系統的DSP+FPGA實現方案

同步序列由48個32位Walsh序列構成,采用了級聯編碼。第一層編碼為沃爾什序列加擾碼。對于沃爾什序列來說,同步情況下的自相關和互相關性能很好。但是在非同步的情況下,沃爾什序列的正交性變差,相關函數有較大的旁瓣值,造成信號間的干擾。為減小旁瓣值,改善Walsh碼的特性,用擾碼乘以沃爾什序列,得到的新碼作為前導序列的內碼,則相關性能得到改善。第二層是對Walsh序列與48個相位組合的相乘,其中48個相位組合為 /4,3 /4,- /4,-3 /4的排列組合。經Matlab仿真取一組使所得到的相關峰較為理想,如圖2所示。

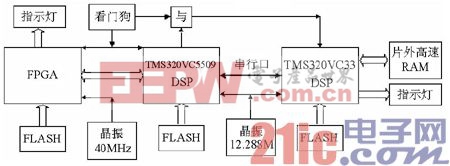

本系統采用TI公司的高性能浮點數字信號處理器TMS320VC33和定點的TMS320VC5509兩片DSP芯片作為系統的中央CPU,并采用ALTERA公司的Cyclone系列F

PGA設計出高速數字相關器,用于前端的信號同步與捕獲,三個芯片協同工作,并以此為主體架構系統的整個硬件工作平臺。

主要芯片介紹

TMS320VC33是TI公司推出的高性能浮點運算DSP芯片。由于其較高的性能價格比,使其應用較為廣泛。它的結構允許它以定點的速率完成浮點操作,因此非常適合于做高速高精度的浮點運算,這一優點對于像短波信道快速估值等實時性精確度要求特別高的數字信號處理應用顯得尤為重要。TMS320VC5509處理器是TI公司最新推出的高性能低功耗定點數字信號處理器TMS320C55x系列中的一員。TMS320C55x系列是在C54x系列的基礎上發展起來的,能與C54x兼容,不僅增加了硬件資源,也優化了資源管理。

TMS320VC5509運行速度快,還可以進行多種并行操作,片內外設資源也比較豐富,與外圍設備的連接很方便,所以非常適合用來作控制用。根據上述兩種處理器的特點,綜合考慮系統的設計要求,我們把TMS320VC5509作為系統的主處理器,而TMS320VC33作為其協處理器。

本文是采用Cyclone系列芯片來實現數字相關器對采樣點值進行一次相關,將相關結果送給中央處理器DSP,進行下一步的同步和解擴等處理。ALTERA公司的Cyclone器件具有專用電路,可以實現雙數據率(DDR)SDRAM和FCRAM接口。Cyclone器件最多有兩個鎖相環(PLL),共有六個輸出和四種層次化結構,為復雜設計提供了強大的時鐘管理電路。

系統硬件模型框圖及概述

首先從電臺接收過來的基帶擴頻信號是差分輸入的,先經過一個1:1的隔離變壓器變為單端輸出,再經過運放將其抬高到直流電平以上,低通濾波后送到模數轉換器AD7492進行采樣處理,采樣結果在FPGA中鎖存,并在FPGA內部進行希爾伯特變換和相關處理。在一個樣點間隔內,進行當前樣點值的希爾伯特變換,同時并行地進行前一個樣點的相關運算。將相關結果分成四個部分,鎖存在對應的四個地址中,由TMS320VC5509分四次依次讀取。由TMS320VC5509和TMS320VC33完成信號的捕獲和碼元的判決。將處理好的數據通過TMS320VC5509送到數模轉換器TLV5619中進行數模轉換,轉換得到的模擬信號經過低通濾波和運放放大以后,再通過同樣的一個1:1的隔離變壓器變為差分輸出送到擴頻電臺。如圖3所示為系統的核心部分。

評論