基于FPGA的SRAM自測試研究

4 SRAM自測試電路的實現

SRAM自測試電路是為了檢測存儲器的好壞和修復錯誤存儲單元而對其進行自檢的。文中自測試電路是由FPGA構成,通過響應計算機系統的控制信號,由其產生一套完整的自檢測試電路。

4.1 硬件描述語言

測試電路的產生可以通過硬件描述語言Verilog編程實現。用Verilog來進行電路設計,設計者可以進行各種級別的邏輯設計,以及數字邏輯系統的仿真驗證、時序分析、邏輯綜合。它是目前應用最廣泛的一種硬件描述語言。

采用硬件描述語言進行設計時,由于硬件描述語言的標準化,可以很容易地把完成的設計移植到不同廠家的不同芯片中去,并在不同規模應用時較容易地作修改。它的信號位數是很容易改變的,可以很容易地對它進行修改,來適應不同規模的應用。在仿真驗證時,仿真測試矢量還可以用同一種描述語言來完成,因為采用硬件描述語言綜合器生成的數字邏輯是一種標準的電子設計互換格式(EDIF)文件,獨立于所采用的實現工藝。有關工藝參數的描述可以通過硬件描述語言提供的屬性表達,然后利用不同廠家的布局布線工具,在不同工藝的芯片上實現。

4.2 系統硬件

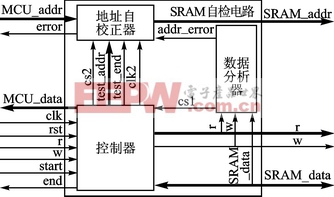

計算機系統包含有多個外圍設備,在本系統中計算機與SRAM之間的通信通過FPGA來傳遞,計算機對FPGA的操作也就是對SRAM的操作。系統硬件電路結構框圖如圖1所示。

圖1 系統硬件電路結構框圖

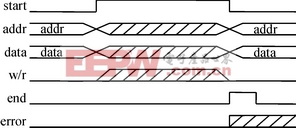

圖中的start信號線是測試啟動信號,上升沿有效;end信號線是測試結束信號線,上升沿有效;error是SRAM故障信號,高電平有效;addr為地址總線;data為數據總線;r/w為讀/寫信號線。系統時序圖如圖2所示,其中陰影部分為未知區域。

圖2 系統時序圖

在系統正常工作時,計算機系統首先將地址信號、數據信號和讀寫控制信號傳至FPGA,通過FPGA內部電路進行處理后將信號傳遞到SRAM端;當start信號線有效時,FPGA啟動自檢電路對SRAM進行故障檢測,并進行故障自校正;測試結束后輸出end有效信號,對于無法修復的故障則使error信號線有效。

4.3自檢電路硬件設計

由FPGA構成的自檢電路主要包括檢測控制電路、數據分析器和地址自校正器等部分[8],是對SRAM進行檢測的關鍵。SRAM自檢電路系統結構框圖如圖3所示[910]。

圖3 SRAM自檢電路系統結構框圖

測試電路工作機制為在start信號有效時,自檢電路進入自檢狀態[11],自檢模塊的控制器部分首先通過使能信號cs1啟動地址校正器內的自檢電路,屏蔽MCU_addr信號使test_addr、test_end和clk2工作;同時通過cs2啟動數據分析器,控制器具有產生地址和測試向量的電路,測試地址通過地址校正器輸出,測試向量通過SRAM_data數據線輸出,通過控制線r/w進行SRAM的讀寫,并通過數據分析器將讀到的數據進行分析;若有故障,則通過addr_error信號線通知地址校正器進行校正。在控制器按照March C算法進行測試完畢后,通過test_end信號線通知地址校正器,并使使能信號cs1和cs2無效。地址校正器接收到結束信號后,將故障單元映射到備用的SRAM存儲單元,若出現故障單元超出備用部分個數或其他無法完成映射的情況,則地址校正器輸出error信號。自檢模塊故障檢測完畢后進入正常工作狀態。

5 結論

本文簡要地介紹了在SRAM中常見的若干故障模型,以及常用的測試方法, 最后提出了一種運用由FPGA構成的存儲器自測試電路對SRAM進行檢測的方法。該檢測模塊不僅具有對存儲器故障檢測的功能,而且還能將產生故障的單元進行自校正,保證系統的穩定運行。當系統有無法修復的故障時,該模塊會發出故障信號。通過SRAM自檢測電路的設計既提高了系統的穩定性,又大大地降低了系統的故障率。該系統測試電路由硬件描述語言編程而來,所以測試電路具有很強的靈活性,便于以后的進一步設計。本文引用地址:http://www.104case.com/article/189704.htm

評論