10G以太網光接口的FPGA實現

4 設計驗證

4.1 設計驗證方法

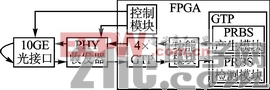

為了驗證該電路設計的正確性,對電路的可靠性進行了測試。在該FPGA設計系統中加入一個偽隨機數列(PRBS)產生和檢查電路。由于Xilinx公司的Virtex6型芯片中的IP核GTP中含有偽隨機數列(PRBS)產生和檢測電路,所以本文采用其內部電路自動生成PRBS并經過整個10 Gb/s的以太網高速數據鏈路,最終由其檢測電路來檢驗數據傳輸中是否出現誤碼。測試方案如圖2所示。FPGA中用于產生和檢測PRBS的GTX核為4個,每一個分別對應一個2.5G鏈路。

圖2 測試方案

由Xilinx公司給出的GTP的用戶說明[9]可知,分別設置信號TXENPRBSTST0、TXENPRBSTST1、RXENPRBSTST0以及RXENPRBSTST1的值為01,而信號INTDATAWIDTH的值為1,其產生的偽隨機數列類型為PRBS7。產生PRBS7數列的多項式為1+X6+X7,數據長度為128,其可以檢驗經過8b/10b轉換的數據。設置信號RXPRBSERR的值為1,以檢測高速數據傳輸過程中數據是否出現誤碼。設置信號PRBS_ERR_THRESHOLD0和PRBS_ERR_THRESHOLD1的值,其含義為PRBS循環檢測中發生錯誤總數的閾值,以控制信號RXPRBSERR(0,1)。信號RXPRBSERR標志著在PRBS循環測試中檢測數據錯誤發生的總值超過了PRBS_ERR_THRESHOLD所設置的閾值,則該信號變為1。產生的PRBS序列經過發送鏈路和外部鏈路環回,再傳輸到接收鏈路,經過相應的處理后到達PRBS檢測電路,進而驗證數據的正確性。其中,外部鏈路環回是主要是指將一根光纖的兩端分別接入到10G光接口的接收與發送端,使數據本身在設計系統中環回。

4.2 驗證結果

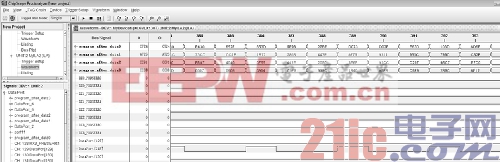

在實驗室常溫環境下,對系統的高速傳輸數據進行驗證。該驗證分為兩個部分,第一部分是運用Xilinx公司研發的軟件工具Chipscope抓取FPGA內部接收和發送的數據進行比較,以驗證所設計的系統是否能實現所要求的功能。Chipscope抓取的結果如圖3所示。信號program_after_data0~3為PRBS產生模塊輸出的數據經過功能模塊處理后的數據。信號RX0_PRBSERR0和RX0_PRBSERR1是第一鏈路中PRBS檢測模塊中RXPRBSERR0、1,由圖可知其值為1,即該系統中第0數據鏈路的錯誤計數沒有超過閾值PRBS_ERR_THRESHOLD的值。由圖可知,信號RX1_PRBSERR0、1,RX2_PRBSERR0、1和RX3_PRBSERR0、1的值均為0,所以系統的4條數據鏈路的錯誤計數均未超過閾值。

圖3 Chipscope系統測試結果

第二部分是運用高頻率范圍示波器抓取FPGA輸出給PHY芯片的數據,以檢測該系統傳輸的信號質量,由示波器測試的數據傳輸眼圖如圖4所示。由于4路2.5G的傳輸鏈路配置相同且篇幅有限,只是列舉出第0路傳輸數據的眼圖。該系統傳輸的眼圖的比特錯誤率(EyeBER)可達到10-45,眼高為600 mV左右。

圖4 高速數據傳輸眼圖

結語

通過反復驗證和長時間連續測試,測試結果證明,該設計能夠有效、正確地實現10 Gb/s的高速數據傳輸,并且傳輸數據的誤碼均未超過閾值,進而證明了該設計系統的可靠性和穩定性。采用FPGA中的RocketIO接口來設計10 Gb/s速率的光纖傳輸,極大地增強了光纖傳輸設計的靈活性,通過修改FPGA代碼即可用于高速信號傳輸的多種情況和場合。

評論