2D-DCT的FPGA實現

在信息社會迅猛發展的21世紀,多媒體信息日益增多,其中人類主要依靠圖像來接收各種各樣的信息。圖像中包含如此巨大的數據量,如果不經過壓縮,不僅超出了計算機的存儲和計算能力,而且無法完成信息的實時傳輸。圖像的高速傳輸和所需巨大的存儲容量已成為數字圖像通信的最大障礙。離散余弦變換(DCT)由于其變換特點被認為是性能最接近K—L變換的準最佳變換,現在已經是最流行的圖像壓縮變換技術,并已經在JPEG、MPEG-1/2/4、H.26x等國際編碼標準中獲得了廣泛的應用[1].由于集成電子技術的高速發展和廣泛運用,數字圖像處理也由軟件向硬件過渡并得到了非常迅速的發展。FPGA作為當今運用極為廣泛的可編程邏輯器件,也是數字圖像處理的理想器件。目前,利用FPGA進行圖像處理主要是直接在FPGA上利用硬件描述語言或EDA軟件進行設計,這種設計方法的最大優點就是速度快,可以利用流水線實現,具有一定的靈活性。

基于行列分解的2D-DCT由于算法規律性強、實現結構直觀、時序控制簡單而被廣泛應用。本文提出使用行列分解法和分布式算法來實現2D-DCT,可以減少硬件資源,提高運算速度,具有一定的現實意義。

1 2D-DCT系統模塊設計

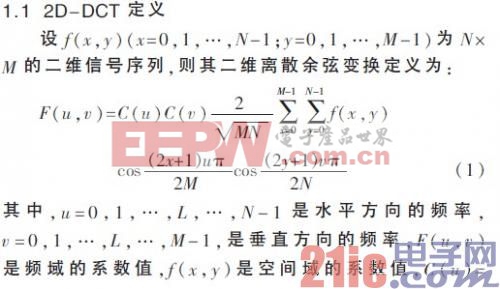

離散余弦變換經常使用在信號處理和圖像處理中,用于對信號和圖像進行有損數據壓縮。這是由于離散余弦變換具有很強的“能量集中”特性,使圖像的主要信息集中在變換后的低頻上,并且能夠去掉像素間較強的相關性,讓圖像的信息集中在少數幾個系數上,以減少冗余達到對圖像進行壓縮的目的。

1.2 系統模塊設計

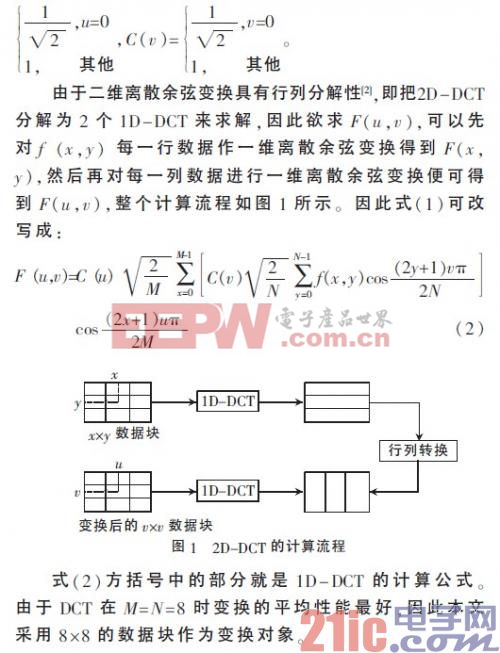

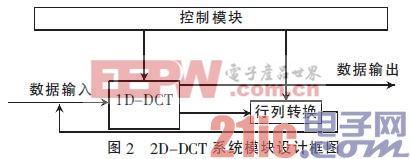

根據2D -DCT 的行列分解性及2D -DCT 的計算流程所設計的系統框圖如圖2 所示, 整個系統由控制模塊、1D-DCT 模塊和行列轉換模塊3 個模塊組成。

在每個時鐘的上升沿從數據輸入端輸入一個數據,8 個時鐘周期后, 輸入的就是8×8 數據塊的一行數據。同時, 控制模塊給1D-DCT 模塊一個信號, 通知它對這8 個數據進行1D-DCT 變換, 并且在計算完之后把結果存進行列轉換模塊中。如此反復8 次后, 就對8×8 數據塊完成了行變換, 所得到的64 個數據依然是以8×8 的矩陣形式存放在行列轉換模塊中。之后控制模塊分8 次從行列轉換模塊中讀出8×8 矩陣的每一列數據, 再送入1D-DCT 模塊中進行變換, 變換后的數據就是8×8 數據塊的2D-DCT 變換結果。

評論