一種紅外解碼IP核在SoPC系統中的設計與實現

紅外解碼IP核包括紅外解碼邏輯和Avalon總線接入邏輯兩個部分,其端口描述如圖5所示。

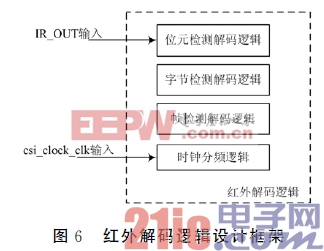

2.1 紅外解碼邏輯的設計

紅外解碼邏輯的設計核心是:采用脈沖計數的方法,檢測IRM-338S接收管輸出的IR_OUT信號在連續兩次跳沿間處于高電平或低電平的時間,進而判斷出每個位元的類型和對應信息,把位元信息組成字節,將字節還原成幀,實現紅外解碼。該邏輯的設計框架見圖6。

(1)時鐘分頻邏輯。在紅外通信協議中,IR_OUT信號在連續2次跳沿間的最小電平持續時間為0.56 ms。為精確檢測該電乎的持續時間,選取周期為40μs時鐘脈沖信號對電平進行計數。該時鐘脈沖信號由Avalon總線的csi_clock_clk信號分頻得到。位元檢測解碼邏輯:檢測IR_OUT信號的跳沿,以跳沿為計數起始和結束點,使用時鐘脈沖信號對位元電平進行計數。位元解碼邏輯將計數結果轉換成位元信息,并輸出位元結束信號。在位元解碼邏輯中,考慮到實際硬件誤差,用不同的計數范圍對應各種位元信息,具體對應關系見表2。

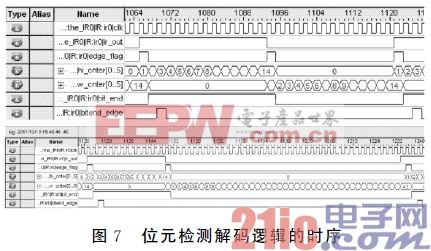

(2)字節檢測解碼邏輯。檢測位元結束信號并進行計數,將連續8個位元的信息填充成1個字節,輸出字節結束信號。幀檢測解碼邏輯:檢測字節結束信號并進行計數,將連續4個字節的信息填充成1個紅外數據幀,輸出解碼結束信號,用于產生中斷;使用SignaltapⅡ對設計的紅外解碼邏輯進行測試,其中位元檢測解碼邏輯時序見圖7。由圖可知,在40μs時鐘脈沖信號下,位元“0”的高電平持續14個脈沖,低電平持續14個脈沖;位元“1”的高電平持續14個脈沖,低電平持續43個脈沖。測試結果與理論分析一致。

評論