基于FPGA的高頻率ADC的實現(xiàn)

數(shù)字系統(tǒng)的設(shè)計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現(xiàn)數(shù)字設(shè)計。除了這些數(shù)字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實現(xiàn)共模功能,從而構(gòu)建模數(shù)轉(zhuǎn)換器(ADC)。

本文引用地址:http://www.104case.com/article/189650.htm與數(shù)字邏輯相連接時,ADC是一種常用的模擬功能塊,例如,F(xiàn)PGA或CPLD連接至模擬傳感器的現(xiàn)實世界時,ADC是不可或缺的。本文將闡述采用萊迪思半導(dǎo)體公司的參考設(shè)計和演示板來實現(xiàn)低頻率(DC至1K Hz)和高頻率(高達50K Hz)ADC。針對每種設(shè)計的應(yīng)用示例,即網(wǎng)絡(luò)交換機中的系統(tǒng).和語音通信系統(tǒng)中的頻率檢測將在文中驗證。

模數(shù)轉(zhuǎn)換器的實現(xiàn)

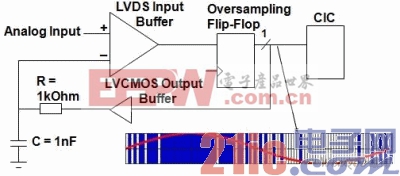

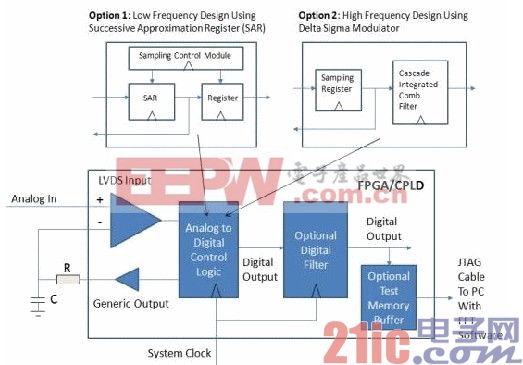

一個簡單的模數(shù)轉(zhuǎn)換器可以通過添加一個簡單的RC電路至FPGA或CPLD 的LVDS輸入來實現(xiàn)。正如圖1的左下角所示,RC網(wǎng)絡(luò)在LVDS輸入的一端,模擬輸入則在另一端。 LVDS輸入將作為一個簡單的模擬比較器,如果模擬輸入電壓高于RC網(wǎng)絡(luò)的電壓,將輸出數(shù)字“1”。通過改變RC電路的輸入電壓(來自FPGA/CPLD的通用輸出),LVDS比較器可用于分析模擬輸入電壓,以創(chuàng)建一個準確的數(shù)字表示。

模擬至數(shù)字控制模塊可以用多種方式實現(xiàn),取決于模擬輸入的頻率、所需的分辨率和可用的邏輯資源。用簡單的逐次逼近寄存器可以處理低頻信號,如圖1左上角的選項1。實現(xiàn)較高頻率的情況如圖1右上角所示,可以用Δ-Σ調(diào)制器功能來實現(xiàn),它由采樣寄存器和級連梳狀(CIC)濾波器組成。

一旦構(gòu)建了數(shù)字信號,就可以對數(shù)字輸出進行可選的過濾,以去除任何由于系統(tǒng)噪音或反饋抖動所引入的不必要的高頻分量。在可選數(shù)字濾波模塊后面,可選的存儲器緩沖區(qū)可用于調(diào)試/測試目的。通過存儲緩沖器對數(shù)字輸出采樣,然后通過JTAG端口掃描輸出,到達運行信號分析軟件的個人計算機。

圖1:模數(shù)轉(zhuǎn)換器基本框圖:低頻和高頻情況。

低頻/最小邏輯ADC實現(xiàn)

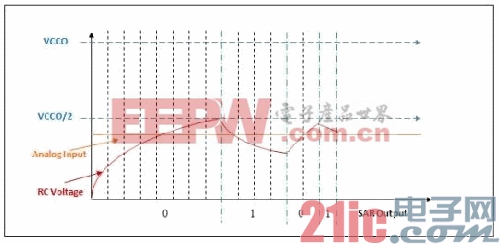

在低頻/最小邏輯實現(xiàn)情況中,采樣控制模塊控制逐次逼近寄存器,相關(guān)的輸出信號隨時加到RC電路。因此RC電路的電壓上升或下降,以響應(yīng)相關(guān)的輸出狀態(tài),輸出狀態(tài)是變化的。LVDS輸入比較模擬輸入與RC電路電壓的變化。因此,RC電路的電壓是用來“發(fā)現(xiàn)”模擬輸入電壓。圖2的例子中,靜態(tài)模擬輸入(由橙色虛線來表示)設(shè)置為不到整個輸入電壓范圍的一半。垂直的黑色虛線表示SAR采樣點之間的時鐘數(shù)目,用綠色虛線來表示。

第一次測量需要8個時鐘,下一次需要4個時鐘,等等類似。最初,通過在相關(guān)輸出上加邏輯“1”,RC電路被設(shè)置為模擬輸入的整個電壓擺幅的一半。一旦電壓達到這個點的一半,LVDS輸入的輸出將指示模擬輸入值是否高于或低于RC電路電壓。

如果模擬電壓較高,數(shù)字輸出的最高有效位是邏輯“1”。如果模擬電壓較低,則數(shù)字輸出為邏輯“0”。SAR移到下一位,采樣時間減半(為整個電壓擺幅的四分之一)。這個過程不斷重復(fù),直到A/D轉(zhuǎn)換器達到所需的精度。在圖2中的例子中,觀察RC電路電壓是如何逐漸接近模擬輸入值。在這個簡單例子中,SAR(0101)的4位數(shù)字輸出展示在圖的底部。

圖2:基于SAR的 A/D轉(zhuǎn)換器運作實例。

低頻設(shè)計可以用來監(jiān)測幾個模擬電壓的電平,這些電平表示各種電源電壓和環(huán)境傳感器的輸出。CPLD實現(xiàn)可以監(jiān)控PCB的電源電壓(3.3V,2.5V和1.8V),以及溫度和濕度傳感器和開放式機箱的報警。為測量多個模擬輸入,可針對每個模擬電壓連同附加的RC電路采用一個LVDS輸入。由于模擬電壓是緩慢改變的,LVDS輸出可多路復(fù)用,這樣在每個輸入之間就可以共享數(shù)字邏輯功能。

低頻/最小邏輯ADC的測試結(jié)果

無需可選數(shù)字濾波電路的低頻/最小邏輯電路已經(jīng)用一塊*估板在萊迪思的MachXO CPLD上實現(xiàn),并使用電壓范圍為0V至3.3V的0.8Hz輸入信號。如圖1所示,采用可選的存儲器緩沖區(qū)及萊迪思ispLEVER設(shè)計軟件的Reveal Logic Analyzer功能。該功能將緩沖存儲器添加至目標設(shè)計,并加入控制數(shù)字信號采集、數(shù)據(jù)緩沖和通過JTAG電纜輸出數(shù)據(jù)到計算機所需的邏輯。在測試過程中,使用Linear公司的PScope軟件在捕獲的數(shù)據(jù)上運行FFT。該電路對0.8Hz模擬輸入的響應(yīng)顯示在圖3的上半部分。

圖3:A/D轉(zhuǎn)換器的結(jié)果實例:低頻和高頻選項。

接收到的數(shù)字信號顯示在PScope屏的頂部窗口中。縱軸用來測量代碼步長(0到255),橫軸用來測量采樣(在這個例子中有1024個樣本)。在邊欄的右上角報告頻率,如f1(基本)頻率。FFT的結(jié)果顯示在窗口的下面,根據(jù)它們的dB水平通過縱軸顯示諧波頻率。從FFT產(chǎn)生的關(guān)鍵參數(shù)顯示在右下側(cè)欄,其中包括有效位數(shù)(ENOB)和信噪比(SNR)。這些結(jié)果表明,輸入信號已成功轉(zhuǎn)換為具有好的分辨率和信噪比的數(shù)字信號。

模擬信號相關(guān)文章:什么是模擬信號

fpga相關(guān)文章:fpga是什么

模數(shù)轉(zhuǎn)換器相關(guān)文章:模數(shù)轉(zhuǎn)換器工作原理

交換機相關(guān)文章:交換機工作原理

存儲器相關(guān)文章:存儲器原理

土壤濕度傳感器相關(guān)文章:土壤濕度傳感器原理

評論