基于FPGA的視頻采集顯示系統

為防止視頻圖像數據在采集與顯示存在不同步的情況,在兩極之間構建了FIFO并配合SDRAM以實現對采集數據的暫存,FIFO的寫使能與攝像頭的行同步信號相連,當行同步信號有效時開始寫FIFO,當FIFO空標志位為低時電平表示FIFO中已存入數據,則NiosII開始控制SDRAM從FIFO中讀取視頻數據,這樣操作的特點就是將經過緩存的數據流無停頓地傳送到輸出端,因此適合對時序不連續的像素進行無縫緩沖處理。

1.4 視頻圖像顯示模塊

視頻圖像顯示通過在FPGA中構建的Nios II嵌入式內核實現,Nios II系統可以在設計階段根據實際的需求來增減外設的數量和種類。可以使用Altera提供的開發工具SOPC Builder,在FPGA器件上創建軟硬件開發的基礎平臺,即用SOPC Builder創建嵌入式內核CPU和參數化的接口總線Avalon。在此基礎上,可以快速地將硬件系統與常規軟件集成在單一可編程芯片中。而且,SOPC Builder還提供標準的接口方式,以便用戶將外圍電路做成Nios II嵌入式內核可以添加的外設模塊。這種設計方式,方便了各類系統的調試。

2 系統軟件設計

2.1 軟件模塊介紹

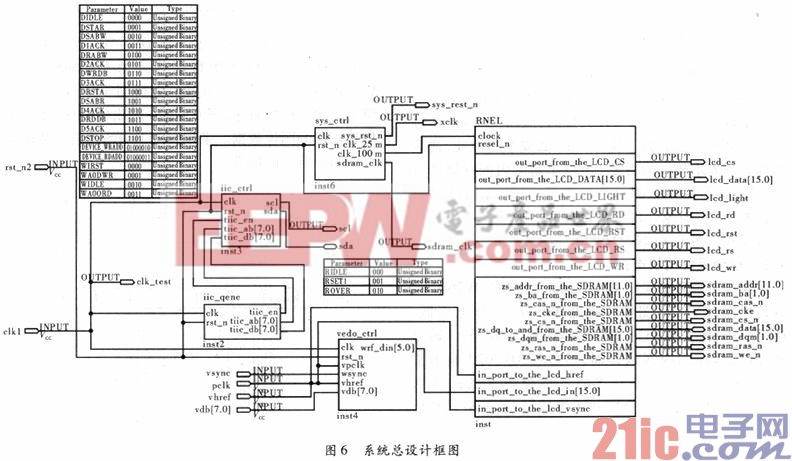

系統軟件總設計模塊如圖6所示,在sys_ctrl中建立PLL鎖相環對時鐘倍頻、分頻產生系統各模塊所需時鐘與系統復位信號,vedio_in put模塊負責OV7670攝像頭的初始化與視頻圖像數據的采集,wrfifo模塊配合Nios II負責對vedio_input采集的視頻圖像數據的緩存,以防止數據時鐘不匹配而出現數據紊亂,而vga_ctrl模塊主要負責產生讀取wrfifo中的數據與實現數據的VGA顯示產生相應的RGB數據與行、場同步信號,再將采集數據送到Nios II中,在Nios II中用C語言驅動TFT液晶,實現視頻數據的顯示。本文引用地址:http://www.104case.com/article/189631.htm

2.2 Nios II嵌入式內核程序設計

Nios II嵌入式內核主要任務是將rag_ctrl采集數據送入SDRAM暫存,然后再根據顯示需要將暫存的數據讀取出來送到LCD顯示,為了確保顯示圖像與采集圖像的一致,在送LCD顯示數據時要注意以下幾點;

(1)根據實際情況去除行、場消隱數據,再根據顯示內容的多少對數據進行裁剪,裁剪到適合LCD顯示的大小,從而避免顯示時圖像的錯位以及亂碼等情況。

(2)由于嵌入式內核時鐘頻率相對于攝像頭的大量數據來說速度還是難以做到攝像頭采集的每幅圖像都能完全顯示,所以在設計中采用隔場采集處理的方式,這樣避免SDRAM中數據過多以至于被填滿的情況,也解決了嵌入式內核采集的出現的卡屏的情況。

3 結束語

采用FPGA設計并實現了一種視頻顯示系統,大幅減少了電路板的尺寸,節約了成本,同時增加了設計的靈活性和系統的可靠性,充分應用FPGA快速并行處理數據的特性,在產生同步信號的同時送出像素數據。嵌入式內核Nios II的使用,解決了其他系統實時圖像顯示的體積與速度問題,擴展了應用范圍。

fpga相關文章:fpga是什么

攝像頭相關文章:攝像頭原理 鎖相環相關文章:鎖相環原理

評論