基于FPGA的帶寄存器尋址SPI接口設計

2.2 SPI接口軟件實現

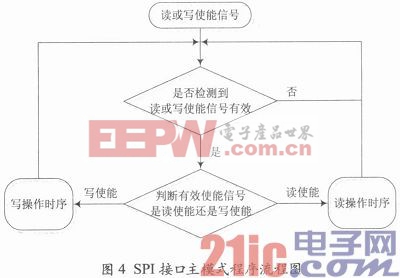

在設計中,采用100 MHz的FPGA內部時鐘FPGA_CLK,而輸出的SPI接口時鐘SCLK為25 MHz。SPI主機控制SPI從機實現讀操作和寫操作的主模式程序流程圖如圖4所示。本文引用地址:http://www.104case.com/article/189595.htm

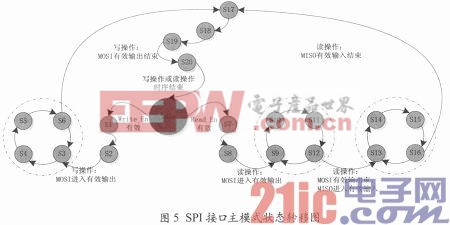

在寫時序和讀時序中可使用同步有限狀態機(FSM)實現其設計,其狀態轉移圖如圖5所示。Idle為空閑狀態時,將檢測寫使能信號Write_ En和讀使能信號Read_En。

當Write_En有效時,進入寫操作時序狀態。在FPGA_CLK時鐘上升沿的控制下,由Idle狀態進入SI狀態,再進入S2狀態,接著進入S3狀態。從S3狀態開始,有限狀態機進入16次循環狀態,循環經過S3、S4、S5和S6狀態。在S3狀態時,SPI主機SCLK輸出低電平,CS輸出低電平,MOSI輸出SPI主機16位移位寄存器的最高位,而移位寄存器左移一位,最低位補0;在S4狀態時,SPI主機SCLK、CS和MOSI輸出保持;在S5狀態時,SPI主機SCLK輸出高電平,CS和MOSI輸出保持,16位移位寄存器的最低位鎖存MISO上的電平;在S6狀態時,SPI主機SCLK、CS和MOSI輸出保持。當16次循環結束時,SPI主機MOSI有效輸出和MISO有效輸入也分別結束。有限狀態機依次進入S17、S18、S19、S20,最后回到Idle狀態,寫操作時序結束。

當Read_En有效時,進入讀操作時序狀態。由Idle狀態進入S7狀態,再進入S8狀態,接著進入S9狀態。從S9狀態開始,有限狀態機進入8次循環狀態,循環經過S9、S10、S11和S12狀態。在S9狀態時,SPI主機SCLK輸出低電平,CS輸出低電平,MOSI輸出SPI主機16位移位寄存器的最高位,而移位寄存器左移一位,最低位補移位寄存器的最高位數據;在S10狀態時,SPI主機SCLK、CS和MOSI輸出保持;在S11狀態時,SPI主機SCLK輸出高電平,CS和MOSI輸出保持;在S12狀態時,SPI主機SCLK、CS和MOSI輸出保持。當8次循環結束時,SPI主機MOSI有效輸出結束,而MISO開始有效輸入。從S13狀態開始,有限狀態機進人下一個8次循環狀態,循環經過S13、S14、S15和S16狀態。在S13狀態,SPI主機SCLK、CS和MOSI輸出低電平,16位移位寄存器左移一位,最低位補0;在S14狀態時,SCLK、CS和MOSI輸出保持;在S15狀態時,SPI主機SCLK輸出高電平,CS和MOSI輸出保持,16位移位寄存器的最低位鎖存MISO上的電平;在S16狀態時候,SCLK、CS和MOSI輸出保持。當8次循環結束時,SPI主機MISO有效輸入結束。有限狀態機依次進入S17、S18、S19、S20,最后回到Idle狀態,讀操作時序結束。

3 SPI接口設計的仿真和綜合

根據上述SPI主機接口的設計方案,可采用Altera公司的Quartus II 8.1軟件對其進行Verilog編程,并在Modelsim SE 6.5軟件中進行時序仿真。SPI接口寫操作和寫操作時序仿真圖如圖6所示。可以看出,當Write_En為高電平時,將1 b讀/寫位、1 b保留位、6 b地址和8 b數據送入SPI主機串行發送緩沖器中。或者當Read_En為高電平時,將1 b讀/寫位、1 b保留位和6 b地址分別送入SPI主機串行發送緩沖器的高8位和低8位中。當下一個FPGA_CLK時鐘的上升沿到來時,將SPI主機串行發送緩沖器的內容送入SPI主機16 b移位寄存器中,接著在FPGA_ CLK時鐘的控制下,進入正常的SPI接口寫操作或讀操作時序過程。當CS為高電平時,產生SPI串行通信結束提示信號SPI_Done_Sig,并將從MISO接收的數據送入SPI串行接收緩沖器。

從以上仿真結果可以看出,本設計可以滿足SPI總線協議的設計要求,且該SPI模塊功能是可以正常工作的。在Quartus II 8.1中完成該模塊的綜合并下載到FPGA開發板上進行驗證。結果表明,本設計可以實現FPGA芯片和從設備間的同步串行通信。

4 結語

本文用Verilog HDL語言以有限狀態機的形式設計了一種符合SPI總線規范的主機模塊,并在仿真軟件Modelsim SE 6.5中進行了仿真,得到的仿真波形符合設計要求。同時,通過在Quartus II 8.1中進行綜合并下載到FPGA芯片中實現了SPI接口功能,也驗證了設計的正確性。該接口可實現SPI主機和帶指定地址控制寄存器的SPI從機間的同步串行通信,具有一定的實用價值。

fpga相關文章:fpga是什么

評論