28nm高端FPGA如何實現功耗和性能的平衡?

實現功耗監控設計流程

從工具的角度看,必須同時考慮功耗和性能。以太高的功耗滿足性能要求,或者功耗較低但是沒有達到性能目標,這都是不可使用的設計。因此,Quartus II軟件還必須能夠在性能和功耗上很好地達到均衡。在沒有用戶干預的情況下,工具會自動只在需要的地方使用高速塊,盡可能降低功耗泄漏以滿足性能要求,同時使得所有其他塊進入低功耗狀態以減小泄漏。此外,還采取了以下降低功耗的措施:

Ÿ 邏輯、RAM 分析、重新規劃,以降低動態功耗

Ÿ 群布局減小了走線長度,降低了動態布線功耗

Ÿ 優化布局以減小時鐘功耗以及非關鍵通路信號布線功耗

建模是重要的步驟,因為它保證了功耗模型的正確性,不是最差也不是最樂觀。公司可以選擇保守、激進或者正確的方式。最終,最適合設計人員的唯一選項是正確地建模。保守選擇導致了估算的功耗在市場上看起來并不具有競爭優勢。激進的選擇導致最終功耗與工具估算的功耗不具有可比性。做到正確的選擇盡可能接近硅片實際測量的功耗,同時滿足了供應商和客戶的要求。

在制造過程中降低功耗,提高性能

提高制造能力,大批量交付器件是提高產量、嚴格工藝的關鍵。Altera早期以標準功耗指標發售器件,以幫助前沿的客戶滿足早期原型開發和生產進度要求,然后,嚴格曲線指標,盡快實現利益,以幫助這些用戶滿足其產品進度和功效目標。Altera采用這一嚴格的工藝來交付低靜態功耗的新L(低功耗)器件。

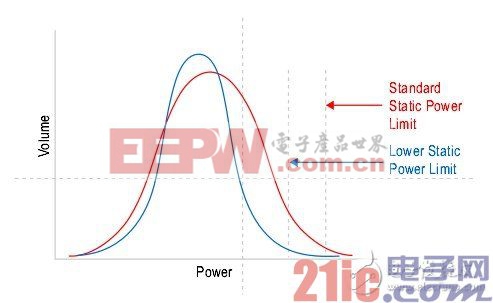

如圖3示,減小工藝變化使得靜態功耗降低了35%,從而降低了總功耗。由于結溫增大和漏電增加是一種指數函數關系,因此,這一方法在較高結溫時極大地降低了功耗,滿足了當今很多系統設計的要求。

圖3 工藝降低了靜態功耗

在28HP制造工藝降低功耗的結果非常顯著,因此,Altera立即將其應用于獨具優勢的FPGA上,在產品代碼中標以“L”。這種突出顯示的訂購碼旨在將產品立即應用于對功耗敏感的設計中,然后,在所有28 nm產品中繼續發揮同樣的工藝優勢。

在FPGA 設計中使功耗和性能達到均衡

設計人員能夠使用高端器件,當這些工具具備了各種低功耗功能以及支持功耗預知的情況下,設計人員自己會確定怎樣均衡其每一設計的性能和功耗。他們從選擇正確的FPGA系列開始。當需要最佳性能或者最大容量時,選用Stratix V FPGA。在Stratix V系列中,可用的型號包括沒有收發器的器件、有收發器的器件,以及重點是DSP應用的器件。

選擇好器件后,在FPGA設計過程中,可以使用幾種設計方法來降低功耗,包括,邏輯和RAM時鐘通道以及部分重新配置等。

即使采用了最佳設計方法、模型和軟件,也只有提供了輸入后才能進行功耗估算。大部分設計人員熟悉基本動態功耗方程:CV2F X (觸發率)。設計工具計算電容(C),已知電壓(V)和頻率(F)是已知的,但是不知道設計的觸發率。確定觸發率的最佳方法是運行代表實際系統使用情況的仿真,得到.vcd文件后,使用PowerPlay功耗分析器工具。次優的方法是為I/O建立合適的觸發率,根據得到的估算,使用 PowerPlay功耗分析器來產生內部觸發率。第三好的方法是使用早期功耗估算器 (EPE),使用以前相似設計的觸發率。最不精確的方法是以默認觸發率使用EPE。功耗估算的精度與默認觸發率和設計實際觸發率之間的差值相關。 Altera建議使用 PowerPlay功耗分析器,通過矢量獲得最佳功耗估算。

設計實例

設計過程中一個重要的早期步驟是,為Stratix V FPGA下載最新的EPE,選擇器件 (功耗指標最低的L器件),為設計輸入信息。與競爭產品相比,Altera的L器件既有動態功耗優勢,又具有總功耗和性能優勢。

下面的例子包括競爭對手以前分析的兩個設計,使用14.2 XPE和Quartus II 12.0SP2 EPE進行了更新,以及一個使用VCC(內核)電源的新例子,針對Altera的雙100G轉發器設計進行了測量和預測。

100GbE OTU4轉發器實例

在這個例子中,運行時用戶相關的結溫是100℃,使用了最大工藝指標。基于競爭對手白皮書中設定的資源使用情況,表3供了I/O和收發器數據,表4提供了輸入到XPE (14.2)和 EPE (12.0 SP2)中的信息。

表3 100GbE OTU4 轉發器 I/O 和收發器信息

表4 100GbE OTU4轉發器資源使用情況

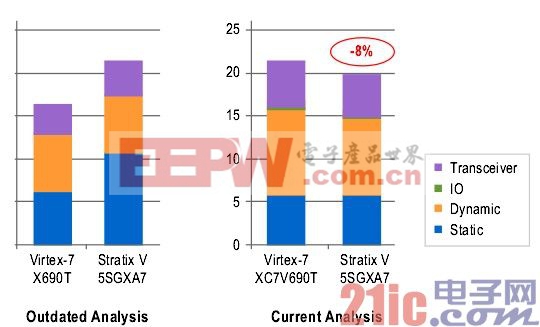

圖4對比了獲得的新L器件結果和以前報告的結果,表明,與Virtex-7 FPGA相比,Stratix V FPGA降低了功耗,同時提高了性能。

圖4 使用L器件,更新后的100GbE OTU4轉發器功耗對比

評論