從實踐角度探討高速PCB的布線問題

接地平面

實際上需要討論的內容遠不止本文提到的這些,但是我們會重點突出一些關鍵特性并鼓勵讀者進一步探討這個題。本文的最后列出有關的參考文獻。

接地平面起到公共基準電壓的作用,提供屏蔽,能夠散熱和減小寄生電感(但它也會增加寄生電容)的功能。雖然使用接地平面有許多好處,但是在實現時也必須小心,因為它對能夠做的和不能夠做的都有一些限制。

理 想情況下,PCB有一層應該專門用作接地平面。這樣當整個平面不被破壞時才會產生最好的結果。千萬不要挪用此專用層中接地平面的區域用于連接其它信號。由 于接地平面可以消除導體和接地平面之間的磁場,所以可以減小印制線電感。如果破壞接地平面的某個區域,會給接地平面上面或下面的印制線引入意想不到的寄生 電感。

因為接地平面通常具有很大的表面積和橫截面積,所以使接地平面的電阻保持最小值。在低頻段,電流會選擇電阻最小的路徑,但是在高頻段,電流會選擇阻抗最小的路徑。

然 而也有例外,有時候小的接地平面會更好。如果將接地平面從輸入或者輸出焊盤下挪開,高速運算放大器會更好地工作。因為在輸入端的接地平面引入的寄生電容, 增加了運算放大器的輸入電容,減小了相位裕量,從而造成不穩定性。正如在寄生效應一節的討論中所看到的,運算放大器輸入端1 pF的電容能引起很明顯的尖脈沖。輸出端的容性負載——包括寄生的容性負載——造成了反饋環路中的極點。這會降低相位裕量并造成電路變得不穩定。

如果有可能的話,模擬電路和數字電路——包括各自的地和接地平面——應該分開。快速的上升沿會造成電流毛刺流入接地平面。這些快速的電流毛刺引起的噪聲會破壞模擬性能。模擬地和數字地(以及電源)應該被連接到一個共用的接地點以便降低循環流動的數字和模擬接地電流和噪聲。

在 高頻段,必須考慮一種稱為“趨膚效應”的現象。趨膚效應會引起電流流向導線的外表面——結果會使得導線的橫截面變窄,因此使直流(DC)電阻增大。雖然趨 膚效應超出了本文討論的范圍,這里還是給出銅線中趨膚深度(Skin Depth)的一個很好的近似公式(以cm為單位):

(5)

(5) 低靈敏度的電鍍金屬有助于減小趨膚效應。

封裝

運算放大器通常采用不同的封裝形式。所選的封裝會影響放大器的高頻性能。主要的影響包括寄生效應(前面提到的)和信號路徑。這里我們集中討論放大器的路徑輸入、輸出和電源。

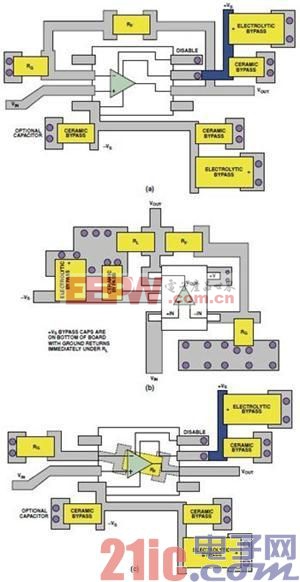

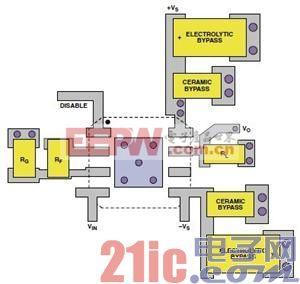

圖 9示出了采用SOIC封裝(a)和SOT-23封裝(b)的運算放大器之間的布線區別。每種封裝都有它自身的一些問題。重點看(a),仔細觀察反饋路徑就 發現有多種方法連接反饋。最重要的是保證印制線長度最短。反饋路徑中的寄生電感會引起振鈴和過沖。在圖9(a)和9(b)中,環繞放大器連接反饋路徑。圖 9(c)示出了另外一種方法——在SOIC封裝下面連接反饋路徑——這樣就減小了反饋路徑的長度。每種方法都有細微的差別。第一種方法會導致印制線過長, 會增大串聯電感。第二種方法采用了通孔,會引起寄生電容和寄生電感。在給PCB布線時必須要考慮這些寄生效應的影響及其隱含的問題。SOT-23布線差幾 乎是最理想的:反饋印制線長度最短,而且很少利用通孔;負載和旁路電容從很短的路徑返回到相同的地線連接;正電源端的電容(圖9(b)中未示出)直接放在 在PCB的背面的負電源電容的下面。

圖9. 同一運算放大器電路的布線區別。(a)SOIC封裝,(b)SOT-23封裝,(c)在PCB下面采用RF的SOIC封裝。

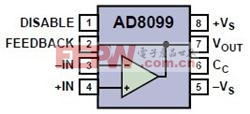

低 失真放大器的引腳排列:ADI公司提供的一些運算放大器(例如AD80451)采用了一種新的低失真引腳排列,有助于消除上面提及的兩個問題;而且它還提 高了其它兩個重要方面的性能。LFCSP的低失真引腳排列,如圖10所示,將傳統運算放大器的引腳排列按著逆時針方向移動一個引腳并且增加了一個輸出引腳 作為專用的反饋引腳。

圖10. 采用低失真引腳排列的運算放大器。

低失真引腳排列允許輸出引腳(專用反饋引腳)和反相輸入引腳之間可以靠近連接,如圖11所示。這樣極大地簡化和改善了布線。

圖11. AD8045低失真運算放大器的PCB布線。

這種引腳排列還有一個好處就是降低了二次諧波失真。傳統運算放大器的引腳配置中引起二次諧波失真的一個原因是同相輸入和負電源引腳之間的耦合作用。 LFCSP封裝的低失真引腳排列消除了這種耦合所以極大地降低了二次諧波失真;在有些情況下最多可降低14 dB。圖12示出了AD80992采用SOIC封裝和LFCSP封裝失真性能的差別。

這種封裝還有一個好處——功耗低。LFCSP封裝有一個裸露的焊盤,它降低了封裝的熱阻,從而能改善θJA值約40%。因為降低了熱阻,所以降低了器件的工作溫度,也就相當于提高可靠性。

圖12 . AD8099不同封裝失真性能對比——相同的運算放大器采用SOIC和LFCSP封裝。

目前,ADI公司提供采用新的低失真引腳排列三種高速運算放大器:AD8045,AD8099和AD80003。

評論