基于FPGA的高速加密卡設計與實現

PCI—E總線接口向主機發送數據的過程:(1)PCI—E總線接口檢測到由FPGA內部發送的啟動PCI—E總線接口信號后,首先向主機發送中斷信號,然后將數據緩存的數據組包后發送給主機。(2)主機接收到PCI—E總線接口的中斷信號后,將PCI—E總線接口發送來的數據存入內存中。(3)PCI—E總線接口發送完數據后再次向主機發送中斷信號,至此PCI—E總線接口向主機發送數據操作完成。

1.2.2 NiosII軟核設計

NiosII軟核處理器是Altera公司推出的第二代集成在FPGA內部的可配置的32位RSIC(Reduced InstructionSet Computer)嵌入式處理器,具有經濟型、標準型和快速型3種,占用少量的FPGA資源,其中快速性NiosII軟核性能較高,速度較快,可獲得超過250DMIPS(Dhrystone Million Instructions executed Per Second)的性能。為使加密卡達到最快的運算速度,本次選用快速型NiosII軟核處理器作為CPU,其通過Avalon總線與SM1算法芯片接口電路、數據緩存、PCI—E硬核接口以及其他接口模塊等互聯,共同組成硬件結構。基于NiosII的軟核處理器采用C語言進行加密卡軟件部分設計,軟件主要功能是根據主機發送的命令控制加密卡完成數據加解密、密鑰管理、權限管理和隨機數生成等操作。同時通過NiosII軟核指令與自定義硬件模塊相結合,以軟硬件協同的方式完成RSA算法電路的設計。

1.2.3 RSA算法設計

加密卡中的RSA算法操作主要包括密鑰生成、密鑰存儲和加解密。到目前為止,密鑰長度為1 024位的RSA算法已經無法保證加密數據的安全性,因此本次加密卡中的RSA算法采用2 048位的密鑰。RSA算法操作中的密鑰生成和密鑰存儲部分需要生成隨機數,并對大量數據進行存儲和轉換,用硬件實現難度大,且效率不高,所以本次采用基于NiosII軟核的軟件方式實現該部分操作。RSA算法中的加解密操作需要對大位數的數據進行模冪運算,運算復雜,雖已有成熟的軟件實現方式,但是該種方法實現的RSA算法運算速度慢,無法滿足設計要求,而硬件實現方式已有成熟的算法,運算速度快,所以本次RSA算法的加解密部分采用硬件方式實現,通過NiosII軟核控制RSA運算模塊完成加解密操作。

模冪運算是RSA加解密的核心,可以通過模乘運算來實現,本次采用蒙哥馬利算法實現模乘運算,該算法利用移位和加法代替了復雜的乘、模操作,易于在硬件上實現。NiosII軟核中定制的RSA加解密運算指令的輸入為密鑰、數據長度和啟動信號,輸出為運算完成信號。當NiosII軟核接收到RSA運算命令后,通過定制的模冪運算指令向RSA運算模塊寫入密鑰和數據長度信號,然后啟動該運算模塊,RSA運算模塊接收到Nios II軟核的啟動信號后,從數據緩存讀取待運算數據進行加解密運算,運算完成后將運算結果存入數據緩存中,并向NiosII軟核發送完成信號,NiosII軟核接收到RSA運算完成信號后啟動PCI—E總線接口,將運算結果發送給主機。這樣采用軟硬件結合的方式實現RSA加解密功能,不但能夠保證RSA運算的正確性,降低RSA算法實現的復雜度,而且比采用純軟件實現方式提高了運算速度。

1.2.4 SM1接口電路設計

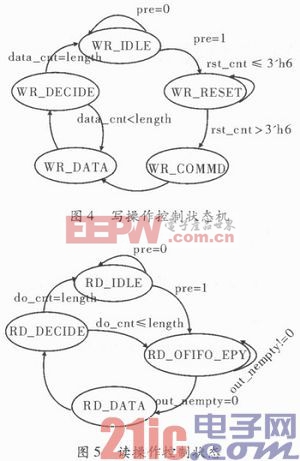

在FPGA內設計有一個專用SM1算法芯片的接口控制電路,用于控制SM1算法芯片實現數據的加解密操作。SM1算法芯片采用雙總線命令和組包操作方式,具有較高的運算速率。所以接口電路主要由寫狀態機和讀狀態機組成,分別控制對SM1算法芯片進行寫數據操作和讀運算結果操作。接口電路的工作原理:加密卡上電后,首先對SM1算法芯片進行硬件復位,然后檢查由NiosII軟核發送的SM1算法啟動信號,若該信號有效,則同時啟動寫狀態機和讀狀態機,這樣能夠在進行寫數據操作時,也讀取運算結果值,從而提高SM1算法命令的執行速率。圖4和圖5分別為寫操作狀態機和讀操作狀態機的設計。

2 設計實現

設計采用NiosII Eclipse開發軟件完成加密卡軟件程序設計,采用QuaxtusII 11.0工具軟件完成加密卡硬件電路設計,并對所設計的軟硬件進行了整合和仿真驗證。在驗證設計的正確性后,完成了對FPGA內部整體電路的布局及綜合,并制作成加密卡樣品。在Windows系統下對所設計的加密卡連續測試168 h,加密卡工作正確;和已有的基于DSP和PCI—E橋接芯片設計的加密卡進行測試比較,結果如表1所示,本次設計的加密卡能夠正確地完成各項功能,同時RSA算法的運算速度為5.9次/s,SM1運算速度為295 Mbit·s-1,較已有加密卡RSA運算的3.5次/s和SM1運算的240 Mbit·s-1有了大幅提高,所以本次加密卡在保證可靠性的同時,運算速度更快。

3 結束語

基于增強信息安全的思想,設計了一種基于FPGA的低成本、高性能的加密卡。采用FPGA內部資源實現了加密卡的控制器模塊、算法模塊、通信接口模塊和各種接口等主要功能。并對兩種不同結構設計方式的加密卡進行了性能比較測試,結果表明采用FPGA單芯片結構設計方式的加密卡功能正確,電路板結構簡單,可靠性強并且具有更高的靈活性和運算速度,達到了預期的目標。目前所設計的加密卡只集成了SM1和RSA算法,今后根據需要,可在FPGA內部通過擴展硬件或軟件的方式來增加其它的加密算法功能,所以,該加密卡實用性強,具有可擴展性,在信息安全領域具有良好的發展前景。

fpga相關文章:fpga是什么

評論