基于FPGA的實時視頻信號處理平臺的設計

水平:f0=g0

f1=2/7 g0+5/7 g1

f2=4/7 g1+3/7 g2

f3=6/7 g2+1/7 g3

f4=1/7 g2+6/7 g3

f5=3/7 g3=4/7 g4

f6=6/7 g4+1/7 g5

垂直:f0=g0

f1=1/4 g0+3/4 g1

f2=2/4 g1+2/4 g2

f3=3/4 g2+1/4 g3

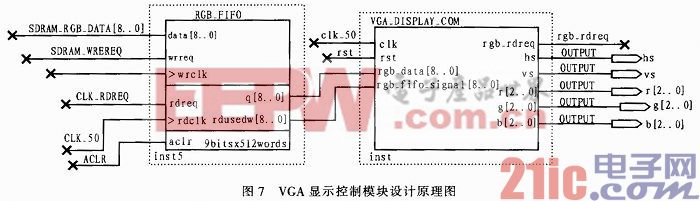

其中g表示原始輸入的像素數據,f表示放大處理后輸出的新像素數據。分辨率提高后的數據再寫入下一級緩存FIFO,然后依次讀入VGA控制模塊,在像素時鐘的同步下輸出給DA進而通過VGA接口顯示在屏幕上。VGA顯示控制模塊設計如圖7所示。本文引用地址:http://www.104case.com/article/189535.htm

2.4 視頻輸出效果圖

圖8所示為本系統采集處理后分辨率為1 024x768的視頻圖像截圖。可以看出經FPGA處理后的圖像比較清晰,可以滿足一般的使用需求。

3 結論

本項目設計的基于FPGA的實時視頻信號處理平臺實現了輸入圖像的格式轉換、彩色空間轉換、幀率提高和像素放大等功能,整個數據流處理過程均在100 MHz的同步時鐘下完成,達到了視頻采集顯示的實時性,且脫離了原始PC機的束縛,實現了系統的小型化,便于推廣和應用。但是本設計也存在一些可以優化的方面,例如可以將圖像輸出分辨率設置成多種模式,通過外部按鍵根據用戶使用需求來控制分辨率的大小,還可以將視頻輸入端改成多通道輸入,對不同區域的視頻信息進行切換顯示或同時顯示。

fpga相關文章:fpga是什么

評論