基于FPGA的PCI數(shù)據(jù)采集卡設(shè)計

2.2.1 總線讀寫設(shè)計

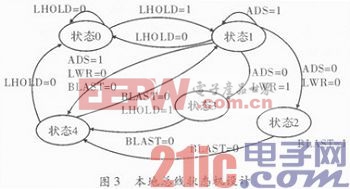

總線讀寫設(shè)計是FPGA設(shè)計的頂層模塊,主要完成PCI9054與本地的通信,實現(xiàn)數(shù)據(jù)的正確傳輸。PCI9054單周期讀、寫和DMA讀的VHDL語言時序控制狀態(tài)機如圖3所示。狀態(tài)0為空閑狀態(tài),狀態(tài)1為總線保持狀態(tài),狀態(tài)2為DMA讀狀態(tài),狀態(tài)3為單周期寫狀態(tài),狀態(tài)4為讀寫操作完成狀態(tài)。本文引用地址:http://www.104case.com/article/189530.htm

2.2.2 控制信號說明

ADS#:地址選通信號,雙向。表示地址有效及新的總線訪問周期的開始,在總線訪問周圍的第一個時鐘周期有效。BLAST#:突發(fā)傳輸結(jié)束信號,雙向。由當前本地總線主動方驅(qū)動,用來表明總線傳輸?shù)淖詈笠粋€數(shù)據(jù)傳輸。LW/R#:寫/讀信號,雙向。低位讀,高為寫。LHOL D:保持總線請求,輸出。請求使用本地總線。當控制可以實現(xiàn)時,本地總線仲裁回應(yīng)LHOLDA。

2.2.3 A/D控制設(shè)計

A/D控制是數(shù)據(jù)采集卡的主要部分,設(shè)計主要包括:A/D采樣時鐘的產(chǎn)生,分組采集控制,觸發(fā)設(shè)置及FIFO讀寫控制等。

(1)A/D采樣時鐘的產(chǎn)生。采樣時鐘的產(chǎn)生主要是根據(jù)設(shè)定的采樣頻率產(chǎn)生具有一定低脈寬的信號,這是為了在轉(zhuǎn)換完成時能正確地讀出轉(zhuǎn)換數(shù)據(jù)。值得注意的是,在FIFO溢出的情況下及分組采集的組間間隔時間段內(nèi)要停止輸出采集脈沖。

(2)分組采集控制。分組采集是按照內(nèi)外時鐘源分別進行設(shè)計的。首先根據(jù)組循環(huán)次數(shù)及首末通道設(shè)置計算出一組內(nèi)總共要采集的點數(shù),即:一組內(nèi)總共要采集的點數(shù)=(末通道-首通道+1)*組循環(huán)次數(shù)。

在內(nèi)時鐘模式下,啟動A/D轉(zhuǎn)換后,在每次轉(zhuǎn)換完成后采集點數(shù)加1,直至加到一組內(nèi)總共要采集點數(shù)為止,此時停止輸出轉(zhuǎn)換脈沖,而后進入組問間隔時間,開始對基準時鐘進行計數(shù),計到設(shè)定的組間間隔值后輸出轉(zhuǎn)換脈沖,再次進入轉(zhuǎn)換計數(shù)周期,依此重復(fù)下去。

在外時鐘模式下,當檢測到外時鐘下降沿時開始輸出轉(zhuǎn)換脈沖并在轉(zhuǎn)換完成后進行計數(shù),直至加到一組內(nèi)總共要采集的點數(shù)為止,此時停止輸出轉(zhuǎn)換脈沖,當再次出現(xiàn)外時鐘的下降沿時,便開始新的一組分組采集。

(3)觸發(fā)設(shè)置。觸發(fā)設(shè)置是根據(jù)板卡控制字中的觸發(fā)源、觸發(fā)方向及觸發(fā)類型共同決定的。

(4)FIFO讀寫控制。FIFO的讀是由PCI9054發(fā)起的,在PCI9054讀周期,在滿足地址條件的情況下,產(chǎn)生FIFO的讀信號,將A/D數(shù)據(jù)傳輸?shù)街鳈C。

FIFO的寫信號是由A/D芯片的STS信號控制的,當STS信號由高變?yōu)榈蜁r表示本次轉(zhuǎn)換完成,且數(shù)據(jù)線上數(shù)據(jù)有效,而FIFO是在下降沿啟動寫周期,上升沿將數(shù)據(jù)打入FIFO中,因此只需將STS信號取反后賦給FIFO的寫信號。

3 硬件設(shè)計的測試

在板卡的設(shè)計過程中,硬件設(shè)計的測試是按如下步驟進行的:首先通過功能仿真及時序仿真排除設(shè)計上的大部分錯誤;其次通過PCItr ee軟件進行測試,通過簡單的功能測試,如開關(guān)量輸入輸出;然后通過簡易演示程序測試;最后通過高級程序的全面測試。在不同的測試階段會發(fā)現(xiàn)各種設(shè)計問題,再將設(shè)計回歸到功能仿真及時序仿真,反復(fù)修改完善程序,直到最終滿足功能設(shè)計要求。

4 結(jié)束語

本文完成了基于FPGA的PCI數(shù)據(jù)采集卡的設(shè)計,板卡實現(xiàn)了查詢、中斷和DMA等多種方式讀取數(shù)據(jù),可實時采集數(shù)據(jù),實現(xiàn)大容量數(shù)據(jù)的緩存,有效地解決對數(shù)據(jù)高速采集和傳輸?shù)男枨蟆?芍苯硬逶赑C機或與之兼容的計算機內(nèi)任一PCI插槽中,構(gòu)成各領(lǐng)域的數(shù)據(jù)采集、波形分析和處理系統(tǒng),也可構(gòu)成工業(yè)生產(chǎn)過程監(jiān)控系統(tǒng)。

fpga相關(guān)文章:fpga是什么

評論