如何快速解決隔離FPGA設計中的錯誤

端口不匹配

設計包含公司內外部提供的文件。在設計中進行IP實例化或預驗證分級模塊時,經常會出現“端口不匹配”錯誤,而且難以檢測,特別是出現在混合語言設計中更是如此。舉例來說,如果頂層VHDL實體“Top”實例化Verilog模塊“sub”,那么頂層VHDL聲明sub有4位端口,而實際Verilog模塊只有3位端口。就Synplify Premier軟件而言,會立即將其標記為不匹配,并在單獨的日志報告中通過超級鏈接引用該錯誤。

視圖work.sub.syn_black_box和視圖work.sub.verilog之間的接口不匹配

細節:

========

源視圖work.sub.syn_black_box中的以下位端口在目標視圖work.sub.verilog中不存在。

=======================================

Bit Port in1[4]

Bit Port in2[4]

Bit Port dout[4]

多級層次中,如何將不匹配問題追蹤到問題模塊的RTL定義呢?工具應以某種方式給所有模塊實例打標簽,比方說采用orig_inst_of屬性。屬性的值包括模塊的原始RTL名稱,可方便地檢索至RTL.例如,假設sub_3s導致端口不匹配錯誤,那么我們就能用以下TCL命令找回RTL模塊的原始名稱“sub”:get_prop -prop orig_inst_of {v:sub_3s}返回值為“sub”。

約束的清除

指定充足且正確的約束將影響到結果質量和功能。約束聲明通常應包括三個元素:主時鐘和時鐘組定義、異步時鐘聲明、錯誤和多循環路徑聲明。

進行綜合之前檢查約束是一個很好的方法。提供約束查看器的工具能發現語法錯誤并分析時序約束和實例名稱是否適用,警示問題所在。比方說,它會報告通配符擴展后約束如何應用以及在定義時鐘約束后產生的時鐘關系。它會標出那些由于參數或對象類型無效或不存在而未被應用的時序約束。

進行綜合之前,在Synplify Pro/Premier軟件中生成名為projectName_cck.rpt的約束檢查器報告:

Synplify Pro/Premier GUI:Run -> Constraint check

或采用TCL命令:project -run constraint_check

注意,要避免潛在的MetA不穩定性,應運行“異步時鐘報告”,提醒您注意那些在一個時鐘域啟動而在另一個時鐘域中結束的路徑。

在Synplify Pro/Premier軟件中生成時鐘同步報告projectName_async_clk.rpt.csv:

Synplify Pro/Premier GUI:Analysis->Timing Analyst并選擇Generate Asynchronous Clock Report選項。

采用TCL命令:set_option -reporting_async_clock

正確的方法是確保您充分且全面地對設計進行約束,而且不會過度約束(過度會導致運行時間延長,生成關鍵路徑錯誤報告)。確保您已完全指定多周期和錯誤路徑,并且已為得到的時鐘設置了約束(set_multicycle_path,set_false_path)。

縮短調試時間

實施潛在的RTL或約束故障解決方案可能需要好幾個小時才能看出結果。我們來看看如何利用分級“分治法”設計方法和“錯誤繼續”功能在單次綜合迭代中發現多個錯誤,從而減少迭代次數。

為縮短運行時間,模塊化流程必不可少。這種流程支持設計保存,能鎖定已經證明有效的設計部分。支持模塊化流程的工具能幫助您在進行綜合前創建RTL分區,也就是編譯點。一些軟件還能幫助設計人員將有故障的設計部分變成黑盒子,徹底將該部分導出并作為獨立的設計子項目進行再加工。一旦解決問題,子項目還能夠以網表形式通過自下而上的流程或用作為RTL通過自上而下的流程整合回原設計,甚至還能綜合利用自上而下和自下而上兩種流程。

要集成和調試大型設計,應盡早在設計進程中發現錯誤的說明。舉例來說,“錯誤繼續”功能可提供涉及每個綜合通過信息的組合錯誤報告。“錯誤繼續”能容許非致命的非語法HDL編譯問題和某些映射錯誤,因此設計人員可在每次綜合迭代中分析并完成盡可能多的設計內容。為了在帶有SynplifyPro/Premier GUI的Synplify Premier軟件中調用“錯誤繼續”功能,應啟用項目視圖左側的Continue-on-Error選項。

在TCL中:set_option–continue_on_error 1

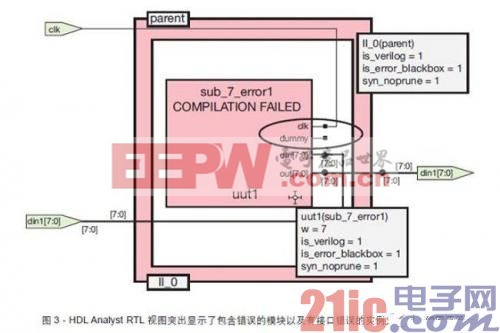

用屬性is_error_blackbox=1標記故障模塊和帶接口錯誤的實例父模塊,如圖3所示。

用TCL找到所有“故障實例”:

c_list[find -hier -inst * -filter

@is_error_blackbox==1]

用TCL列出所有“故障模塊”:

get_prop -prop inst_of[find -hier -inst

* -filter @is_error_blackbox==1]

要查看將被關入黑盒子或導出的故障模塊,請查找HDLAnalyst RTL視圖中的紅色塊(圖3)。

評論