基于FPGA和BU-65170的1553B遠程終端設計與實現

3.1 讀/寫模塊

根據芯片手冊給出的CPU讀寫時序圖編寫程序,在FPGA中實現對BU-65170寄存器和內部RAM進行讀寫的模塊。讀寫模塊的仿真時序圖如圖4和圖5所示。本文引用地址:http://www.104case.com/article/189492.htm

在讀寫過程中,信號BU_RD_WR為‘1’時表示對BU-65170進行讀操作,為‘0’時為寫操作;信號BU_MEM_REG為‘1’時表示對內部RAM進行讀/寫,為‘0’時表示對寄存器進行讀/寫。在零等待模式中,信號BU_STRBD和BU_SELECT(可與BU_STRBD綁定,所以沒有給出)控制著讀/寫操作的開始。

在長STRBD模式下SELECT和STRBD同時為低電平的第2個CLK上升沿,內部鎖存MEM_REG和RD_WR信號;短STRBD模式下STRBD上升沿內部鎖存MEM_REG和RD_WR信號。考慮到容易滿足時序要求,采用長STRBD模式。當BU-65170鎖存住MEM_REG或RD_WR信號后,BU_READY會出現一個上升沿,緊接著當BU_READY出現下降沿時,表示BU-65170內部傳送周期已經結束。

在16位零等待模式下,寫一個內部存儲單元或寄存器時,只需執行一次寫操作,使該字的地址和數據呈現在地址總線和數據總線上即可。而讀一個內部存儲單元或寄存器時,需要進行兩次讀操作。第一次讀時,要讀單元的地址和位置出現在A13-A00和MEM_REG上,這個周期獨處的數據應忽略掉;第二次讀時,相應的數據會出現在數據總線上。

因此,如果FPGA要執行一個多字讀操作,地址總是早于對應的讀出數據,在同一個周期上,地址總線上出現下一個字的地址,數據總線上出現前一個字的讀出數據。

3.2 配置模塊

BU-65170有17個寄存器,通過配置這些寄存器來選擇工作模式和具體功能。選擇增強模式、增強中斷使能模式,使能RT子地址控制字中斷,服務請求自動清除。初始化流程如圖6所示,寄存器詳細配置如表3所示,具體子地址設置如表4所示。

3.3 時鐘模塊

使用40 MHz的外部晶振作為FPGA的時鐘輸入,然后用FPGA自帶DCM模塊分頻得到16 MHz主時鐘,作為其余模塊的全局時鐘,仿真和實際波形測試表明全局時鐘穩定性良好,滿足系統要求。

3.4 RS 422控制及UART模塊

RS 422模塊實現了RS 422通信功能,一方面滿足了工程要求;另一方面也使調試1553B系統變得方便明了,因為1553B發送過來的數據可以立即通過RS 422轉RS 232接口顯示在PC機上,同理,可以通過PC機發送數據到1553B的總線控制器。1553B總線接收數據的過程如下:RS 422端口發送數據到FPGA,將數據緩存在FIFO中,RT接收到發送命令后,FPGA把FIFO中的數據寫入RT相應的發送子地址,最后再由RT發送給BC。類似地,1553B總線發送數據的過程如下:RT接收到接收命令后,FPGA立刻把數據從相應子地址讀出,并傳送給RS 422模塊,再通過UART將數據發出。

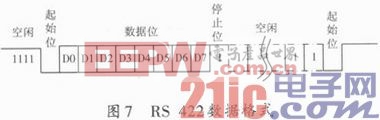

UART采用10位異步通信方式,即1個起始位,8個數據位,1個停止位,如圖7所示,波特率為9 600 b/s。RS 422控制模塊內部包含一個分頻模塊,將產生RS 422接口定義中的收發所需的波特率。通過對于系統時鐘的分頻,產生波特率為9 600 b/s和153 600的信號。

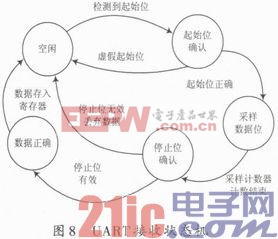

接收狀態機見圖8。當檢測到起始位時,首先檢驗起始位是否正確,如果正確,立即采樣數據位,否則就返回空閑狀態。當采樣計數器計到8后判斷下一位是否為停止位,若不是,則丟棄數據并進入空閑狀態;若是,則把數據存入寄存器后進入空閑狀態,結束一次成功的接收。為了提高正確率,還采用三模冗余算法。UART發送過程與接收類似,在收到發送信號后將需要發送的數據存入緩存,在使能有效和緩存不空的情況下開始傳輸。此時指針開始計數,首先發送起始位‘0’,接著一次發送8 b數據,最后發送停止位‘1’,結束一次發送過程。

fpga相關文章:fpga是什么

評論