基于AD9958多波形雷達信號源軟硬件的設計

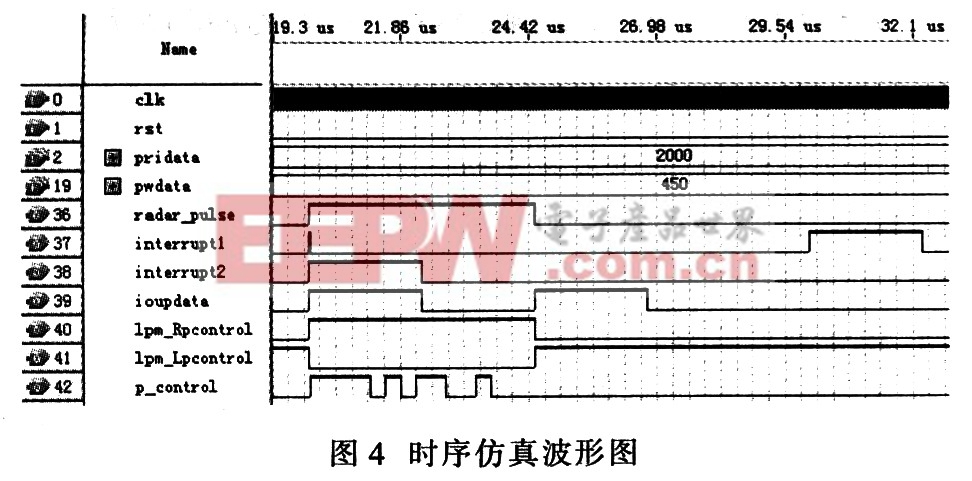

3.3 時序仿真

時序控制在QuartusII7.2軟件下完成,其一個周期內的時序仿真如圖4所示,將10 MHz的dspclk用作脈沖計數時鐘,由于計數時鐘為0.1μs,則計數2 000次相當于200μs。所以設置pridata與pwdata為預置的脈沖重復周期與脈沖寬度值的10倍,則計數后正好是脈沖重復周期和脈沖寬度值。radar_pulse為雷達脈沖,interruptl為引前幀同步,作為DSP中斷1,用于DSP中設置脈內參數;interrupt2作為DSP中斷2,用于設置脈外參數;IOUPDATA為DDS更新信號。在線性調頻方式下,R_pcontrol觸發DDS產生掃頻方向為正的線性調頻信號;L_pcontrol觸發DDS產生掃頻方向為負的線性掃頻信號。在相位編碼方式中,以m15序列碼作為相位控制為例,p_control為相位選擇脈沖,產生m15序列碼11l 101 01100l 000。由圖4的仿真結果可知,其產生的時序與圖2要求的時序相同,從而驗證了系統設計的正確性。本文引用地址:http://www.104case.com/article/189026.htm

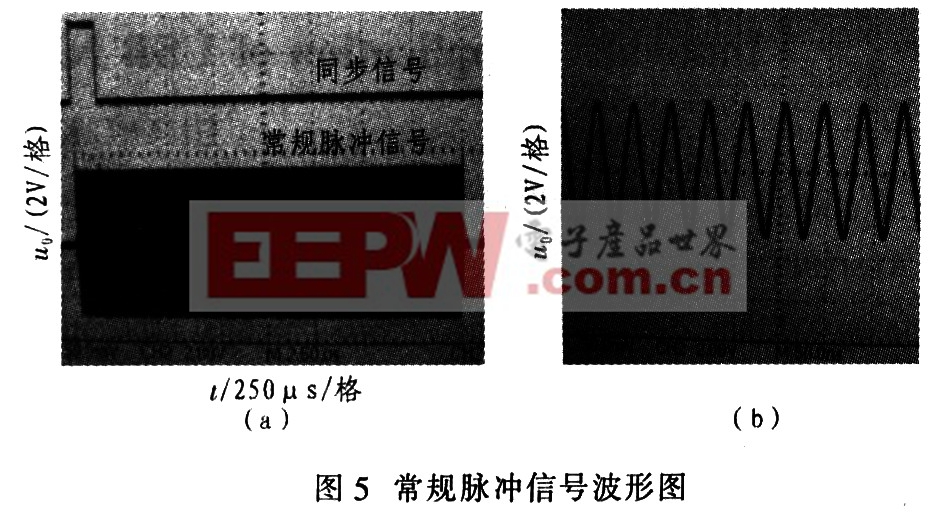

3.4 實驗結果

此系統可方便產生參數可調的常規脈沖、線性調頻、相位編碼脈沖信號,在示波器下觀察得出,利用AD9958設計產生的信號波形精度高。圖5(a)為示波器觀察的脈沖同步信號和常規脈沖信號,圖5(b)為信號局部放大圖。由圖5(a)可看出:u0的脈沖信號為20μs;由圖5(b)可看出:中頻頻率f0=30MHz,脈沖重復周期為1000μs,脈沖寬度為20μs。

4 結語

在介紹DDS芯片AD9958基礎上,介紹了雷達頻率合成器中頻產生模塊,并仿真了其中的FPGA時序控制模塊。該雷達模擬器可靈活配置信號種類、脈寬和重復周期的多種參數,其穩定度高,精度高,分辨率高,且可實現雙路正交輸出。

評論