一種可重構流水線結構模數轉換器的設計

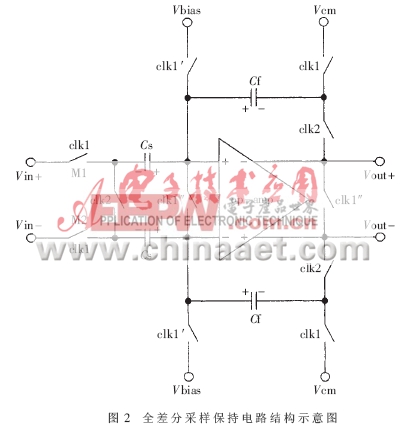

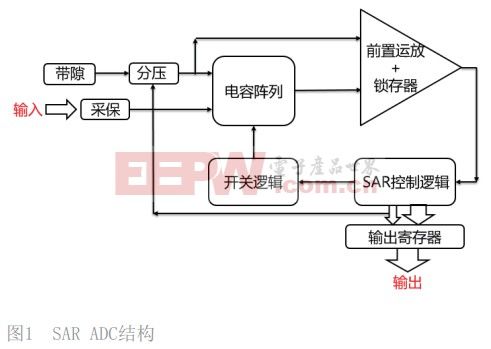

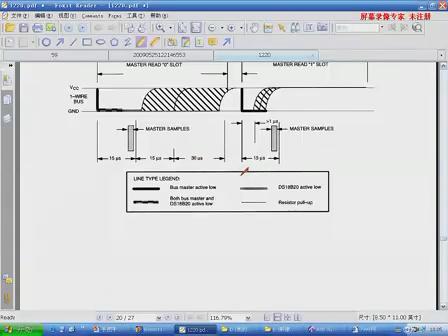

采樣保持電路是流水線ADC中關鍵的模塊。它在采樣周期時,對輸入的模擬信號進行準確采樣,在保持周期時,將采樣結果保持一段時間,即實現模擬信號的離散化,其速度和精度直接決定了整個流水線ADC的速度與精度。本設計中采用了全差分結構底極板采樣電荷轉移結構采樣保持電路,其結構示意圖如圖2所示。該電路使用兩相非交疊時鐘,除了時鐘clk1之外,還存在時鐘clk1′和clk1″,按照clk1′、clk1″和clk1的順序依次閉合,然后再相繼斷開。

根據時鐘,該電路的工作可分為采樣和保持兩個階段。在采樣階段,時鐘clk1、clk1′和clk1″有效,運算放大器的兩個輸入端被短路,電容CS對輸入信號進行采樣并以電荷的形式存儲起來。在保持階段,clk2有效,存儲于CS上的電荷轉移到電容Cf上,從而實現了對采樣電壓的保持。由于采用了全差分結構、相應的時鐘控制以及底極板采樣技術,可以有效地降低開關溝道電荷注入、時鐘饋通、共模電壓、溫度漂移等的影響,提高了電路的精度。此外為了減小由輸入采樣開關M1、M2的非線性導通電阻引入的非線性,還采用了柵壓自舉電壓控制的NMOS采樣開關以改進采樣開關的線性度,提高精度及輸入信號的范圍。

2.2 運算放大器

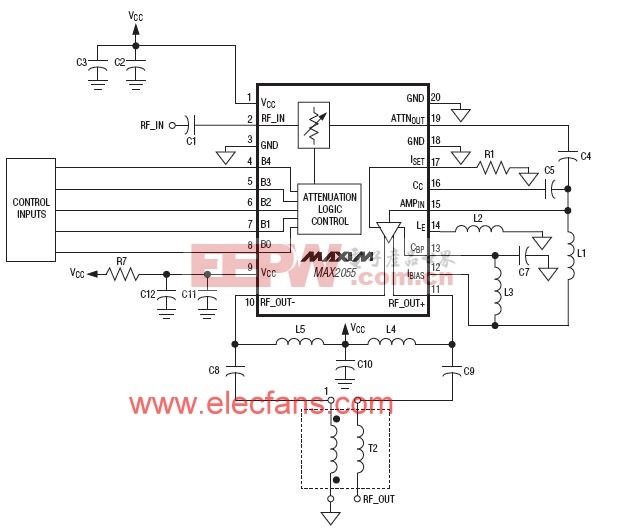

運算放大器是采樣保持電路的核心,其性能直接影響采樣保持電路的速度和精度,是流水線ADC電路設計的關鍵。本設計采用共源共柵兩級運算放大器[4],其第一級采用高速的套筒式共源共柵運算放大器來彌補兩級運算放大器速度慢的缺點,因此整個電路具有相對較高的增益、較高的速度、較低的功耗和噪聲及較大的輸出擺幅等特點,其電路結構如圖3所示。

由于在第一級中采用了共源共柵(cascode)結構,極大地提高了第一級的輸出阻抗,具有較高的增益。其直流增益可表示為:

評論