一種通用中頻數(shù)字化接收機的實現(xiàn)

3 測試結(jié)果和分析

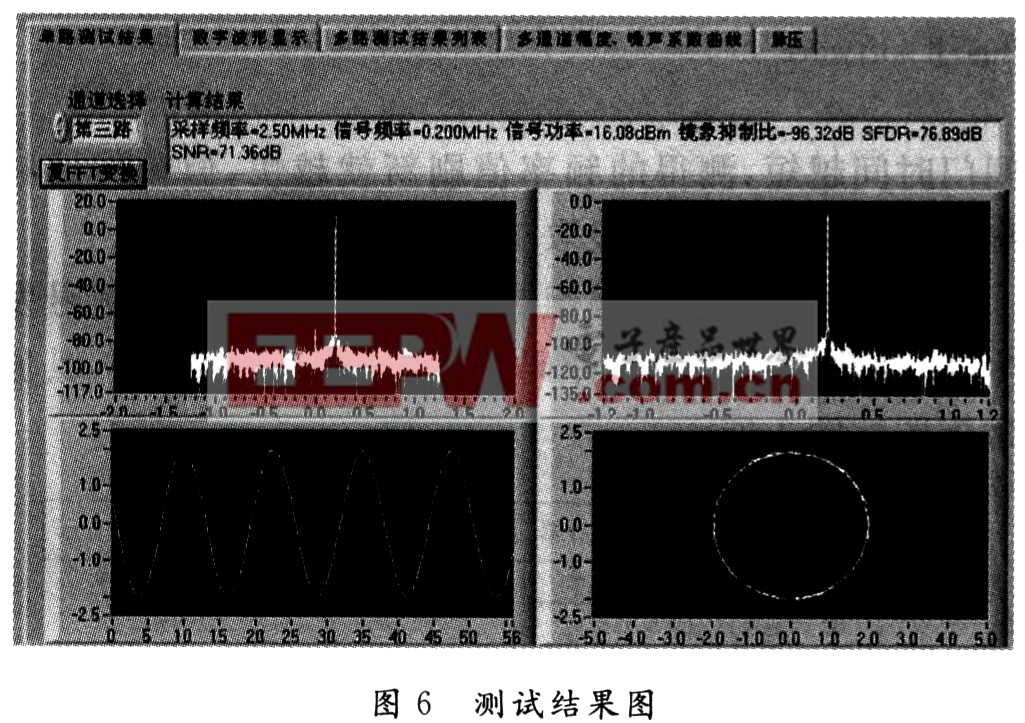

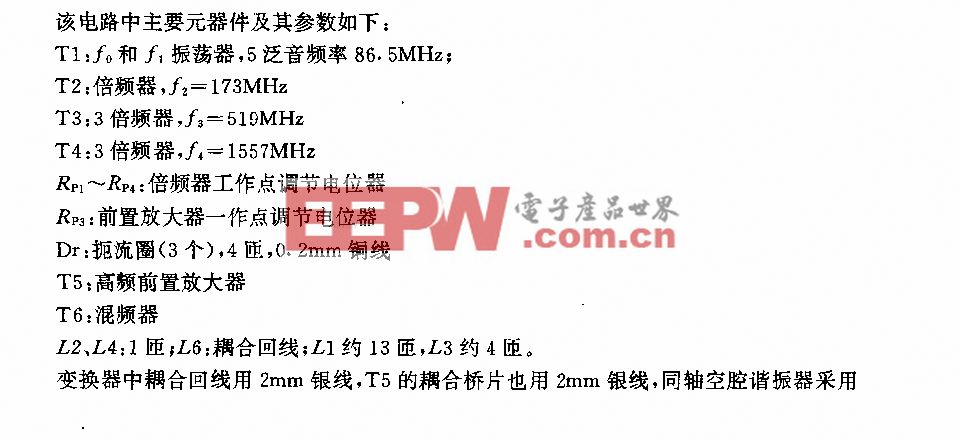

利用圖形化編程軟件LabVIEW設(shè)計一套系統(tǒng)指標測試程序,用該程序?qū)Σ杉臄?shù)據(jù)分析后結(jié)果如圖6所示。圖6所示的是80 MHz系統(tǒng)采樣時鐘,輸入信號是10.2 MHz的單點頻信號,輸出為2.5 MSPS數(shù)據(jù)率。可以看出,信噪比(SNR)為71 dB,無雜散動態(tài)范圍(SDFR)為77 dB,鏡像抑制比為96 dB。這說明I,Q的正交度高,這一點是模擬中頻接收機無法比擬的。

該中頻數(shù)字接收機可處理信號帶寬達到20 MHz以上,因此能夠滿足通訊和雷達系統(tǒng)的一般要求,雖然現(xiàn)在流行用FPGA設(shè)計數(shù)字接收機,但大容量、高速的FPGA價格昂貴。另外,軟件設(shè)計也較復(fù)雜,而ISL5416功能強大,設(shè)計靈活,價格適中,因此ISL5416相對FPGA設(shè)計具有較大的性價比優(yōu)勢。但在使用時,要注意的是,ISL5416輸出數(shù)據(jù)具有不可恢復(fù)性,若工作時鐘受干擾或中途切換,輸出數(shù)據(jù)將出錯。

ISL5416提供的兩個信號RESET是復(fù)位信號,SYNCin是全局同步信號,RESET有效使整個芯片停止工作,所有寄存器置默認值,而SYNCin有效則刷新NCO控制字,抽取計數(shù)器,則重新啟動濾波器。輸出數(shù)據(jù)計數(shù)器時鐘和混頻濾波通道時鐘是兩個支路時鐘。因此,系統(tǒng)電路的時鐘和同步信號受干擾或中途切換,最好用RESET復(fù)位,再重新加載數(shù)據(jù)工作,不能簡單用SYNCin來復(fù)位。

4 結(jié) 語

目前,中頻數(shù)字化接收機已在通訊和雷達產(chǎn)品中普遍運用,產(chǎn)品的通用性、可靠性、可移植性代表了產(chǎn)品的生命力,也符合軟件無線電的思想。本設(shè)計的電路能夠較好地實現(xiàn)中頻數(shù)字接收機的總體指標,已在多個雷達產(chǎn)品中實現(xiàn)中頻直接采樣,而且也實現(xiàn)了米波段射頻直接采樣數(shù)字下變頻,性能穩(wěn)定可靠,實時處理性強。

評論