一種通用中頻數(shù)字化接收機的實現(xiàn)

時序控制和信號預處理芯片采用Altera公司的A-PEX系列的一款器件。該芯片包括典型的200 000個邏輯門,片內帶有邏輯存儲單元,具有106 496 b RAM。運算速度和內部資源能滿足時序控制和一般信號處理的要求。這個系統(tǒng)的時序控制電路采用Verilog硬件描述語言編程實現(xiàn)。

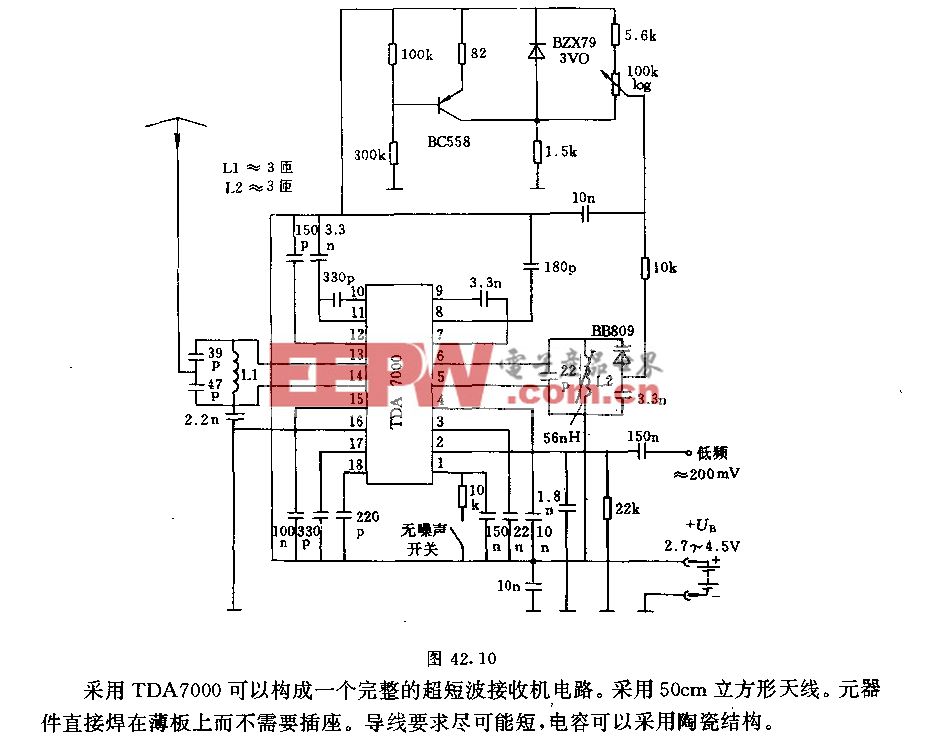

本系統(tǒng)采用AD6645實現(xiàn)模數(shù)變換,用ISL5416完成數(shù)字下變頻,用FPGA進行時序控制,再配以外圍電路構成中頻數(shù)字接收機電路。用AD6645結合ISL5416是靈活設計中頻數(shù)字接收機具有較高性價比的組合。

本設計的主要工作是ISL5416的參數(shù)選取,主要是數(shù)字下變頻器芯片ISL5416的NCO和數(shù)字濾波器的參數(shù)設計和設置。NCO的頻率設置范圍為-109~+109Hz,本設計NCO選用10 MHz。中頻信號經Mixer混頻后,需經抗混疊濾波,首先是CIC濾波器,其后是2級FIR濾波器。CIC一般采取5級級聯(lián),5級級聯(lián)可滿足雜波抑制的一般要求。其后第一級FIR濾波器主要是進一步降低CIC后數(shù)據(jù)率,最大化FIR2的效能,F(xiàn)IR2提供最終的濾波效果。中間包括三次抽取。一般抽取器放在濾波器之后,這樣即可濾除高頻分量,又可確保輸出不混疊。圖2是濾波器通道流程圖。本文引用地址:http://www.104case.com/article/188825.htm

FIR濾波器可借用專門的濾波器設計軟件或Mat-lab軟件設計。抽取因子的選取根據(jù)不同采樣率或數(shù)據(jù)率進行選取,總抽取因子為各因子相乘,三個抽取器抽取比的選取,一般考慮將大抽取比放在CIC處,因為CIC只做位和加法運算,不做乘法運算,適合實時處理,靈活方便。經過大抽取后降低了后面FIR濾波器設計的壓力。最后經濾波,抽取后總效果應做到心中有數(shù),用Matlab進行仿真,以檢驗各濾波器設計是否合理。

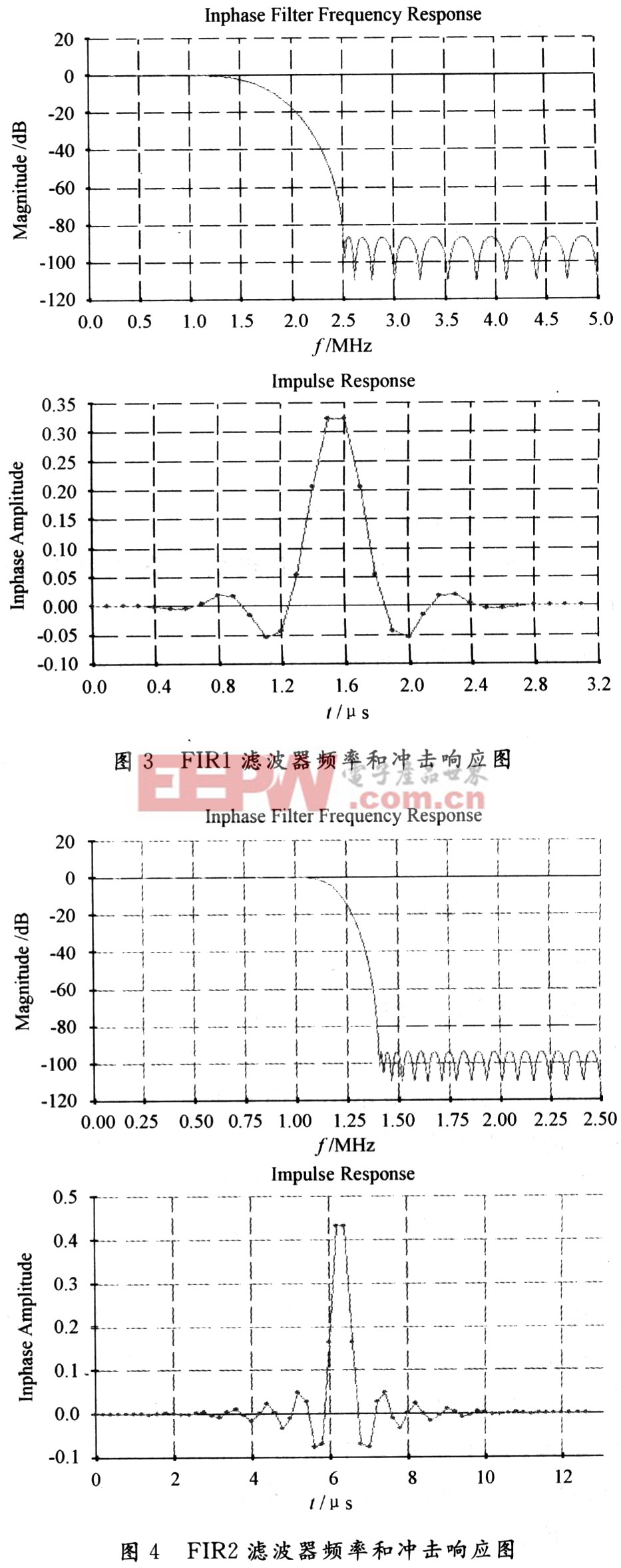

本設計濾波器考慮用5級CIC級聯(lián)后8級抽取;32階FIR濾波器后2級抽取;64階FIR濾波器后2級抽取。這樣的總抽取也實現(xiàn)了2.5 MSPS輸出數(shù)據(jù)率。對于FIR1濾波器的設計參數(shù):經8級CIC抽取后,其數(shù)據(jù)率為10 MHz。選定32階的FIR濾波器的參數(shù)是:采樣率10 MHz,通帶1 MHz,止帶2.5 MHz,通帶起伏0.01 dB,阻帶衰減80 dB,設計結果如圖3所示。

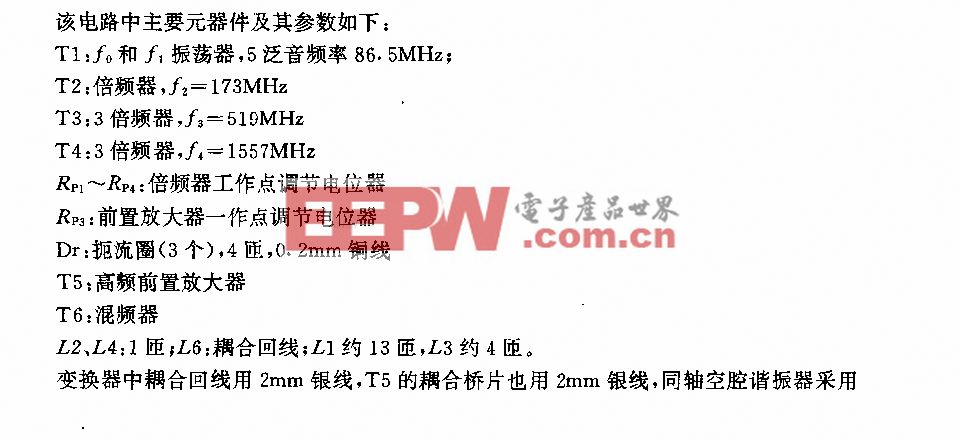

對于FIR2濾波器設計參數(shù):經2級FIR1抽取后,其數(shù)據(jù)率為5 MHz。選定64階FIR濾波器的參數(shù)是:采樣率5 MHz,通帶1 MHz,止帶1.4 MHz,通帶起伏O.01 dB,阻帶衰減80 dB,設計結果如圖4所示。

ISL5416經8級CIC濾波抽取,2級32階FIR濾波抽取,2級64階FIR濾波抽取后總效果用Matlab軟件仿真如圖5所示。圖中顯示了3個辛格函數(shù)(sinc)的旁瓣。從圖5可以看出,帶外抑制在90 dBFS以下能夠滿足實際要求。

評論