基于FPGA的多路模擬信號源設計

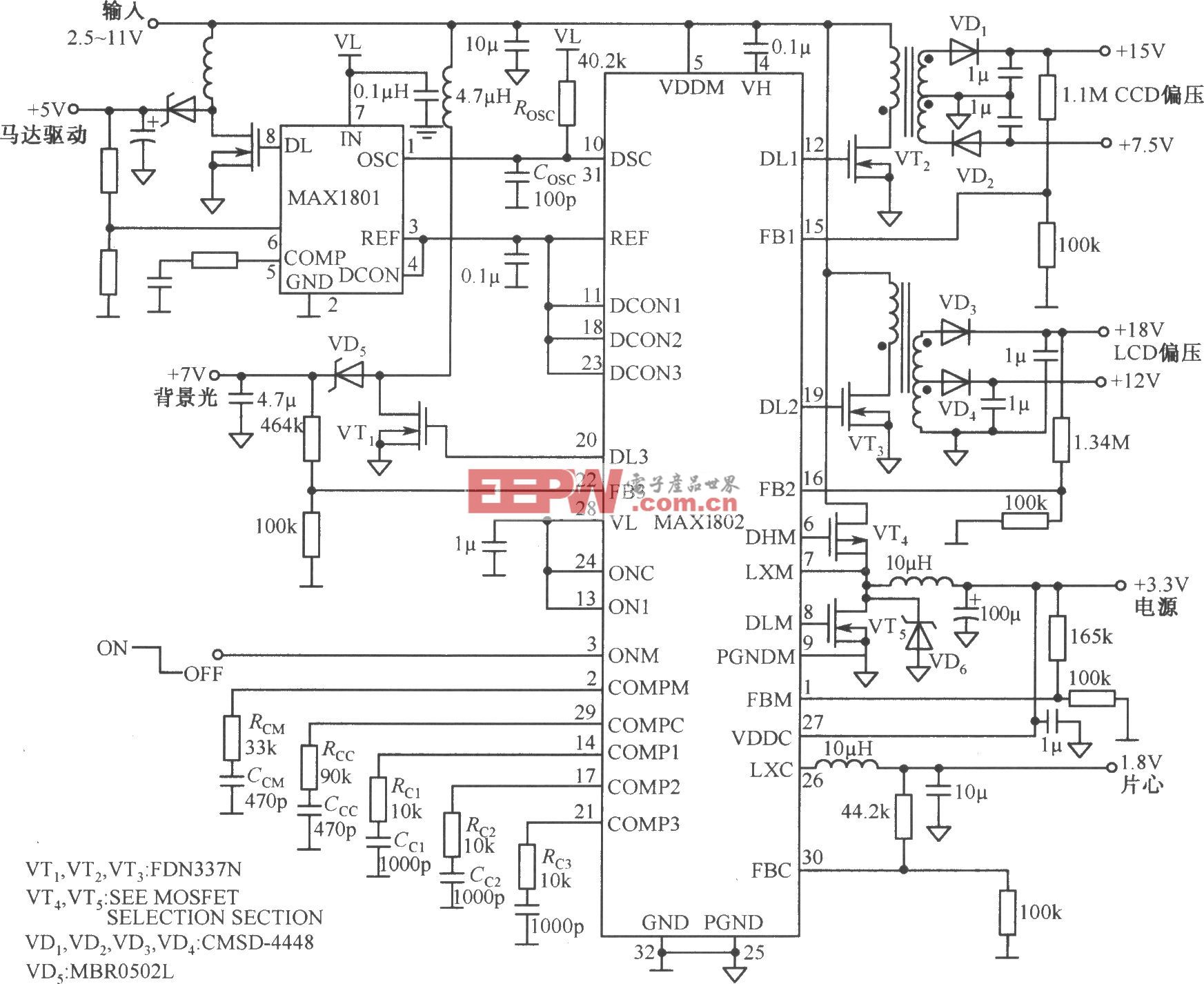

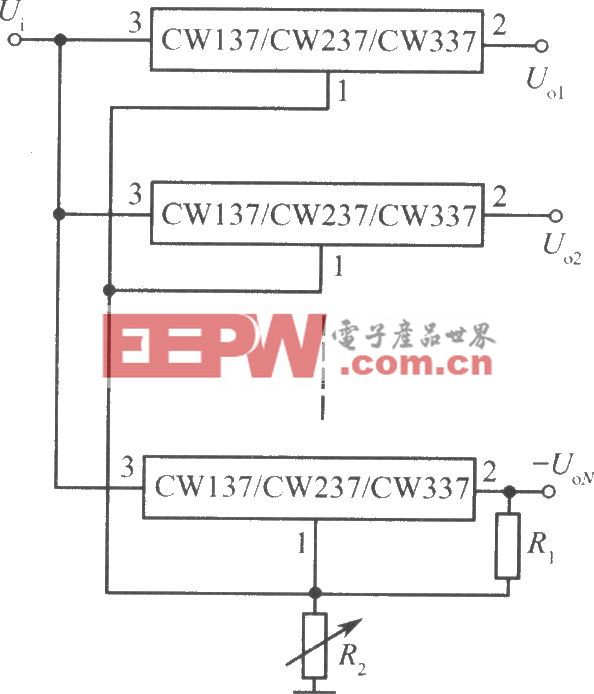

2.2.2 前端穩壓單元

REF198精密電壓基準,初始精度0.05%,溫漂5ppm/℃,輸出電流30mA,最大電源電流45 μ A,電源電壓范圍6.4V~15V,輸出電壓4.096V,每路輸出電壓與理論設置值的誤差在30mV以內;每路驅動能力不低于5mA;該芯片同時為數模轉換(DAC)模塊和運放模塊提供工作電壓。

2.2.3 DAC單元

MCP4821是12位DAC芯片,本文中是單電源供電,32.768 MHz時鐘支持的SPI接口,溫漂50ppm/℃,電源電壓范圍2.7V~5.5V,內部參考電壓為2.048V,FPGA向MCP4821寫入16位數據,如圖3所示,高四位是芯片配置位(Config bits),其它12位是數據位(data bits),在CS信號上升沿有效時,經過16個時鐘脈沖完成轉換。本文引用地址:http://www.104case.com/article/188747.htm

2.2.4 運算放大單元

AD824運算放大器是美國AD公司生產的單電源、低功耗、精密場效應輸入的運算放大器。采用雙電源工作時,它的輸出電壓能夠達到電源的正負電源電壓。AD824的芯片內含有四個性能匹配的運算放大器。在本設計的雙電源工作時,額定工作電壓由±1.5v到±18v。它們的輸出電壓擺幅僅比電源電壓小10mV。輸入信號有可能出現大于+VS時,運算放大器的同相輸入端串聯一個電阻,典型值為1k Ω,就能防止輸入信號的相位反相,但將產生附加的輸入電壓噪聲。

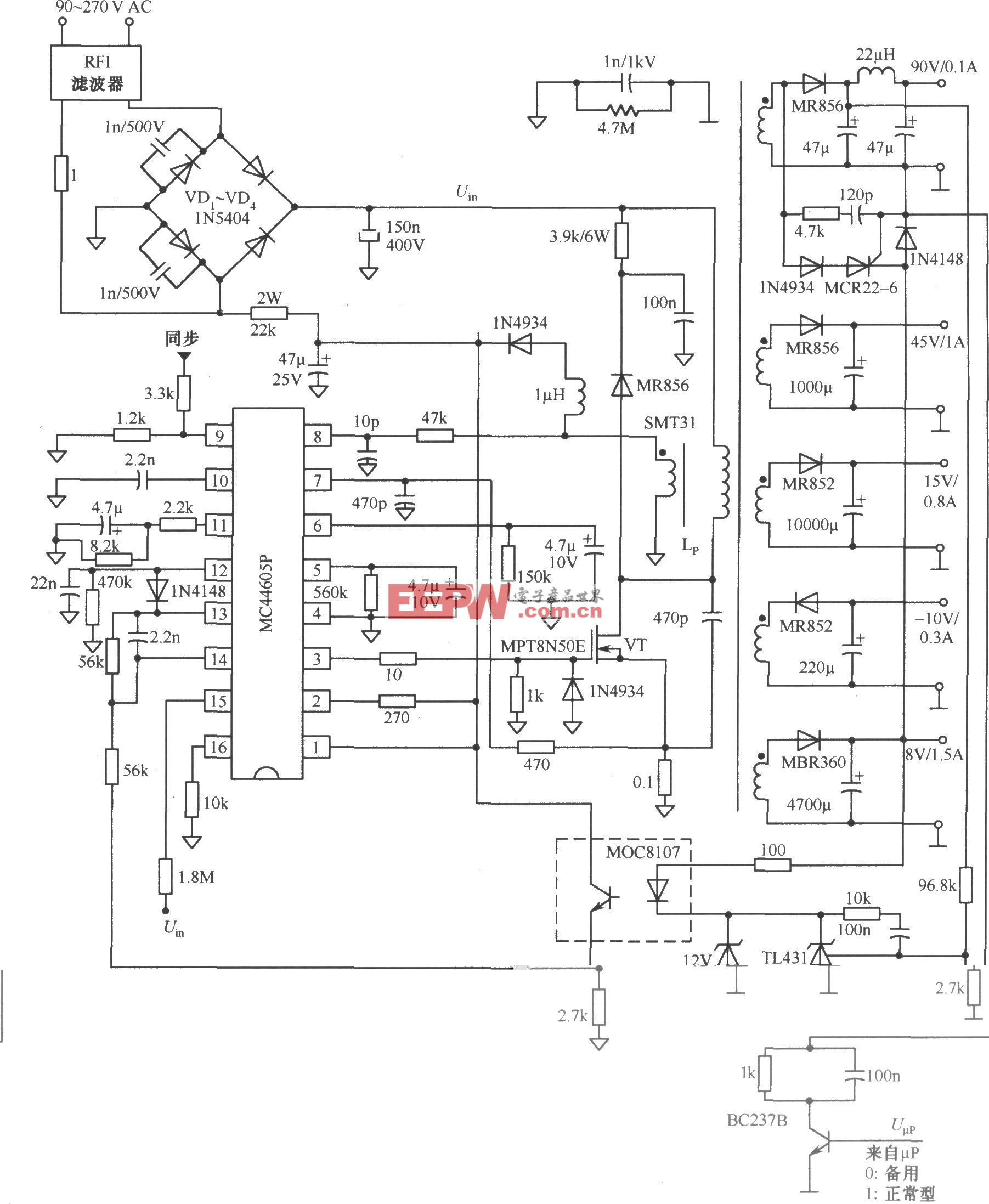

3 電磁干擾設計

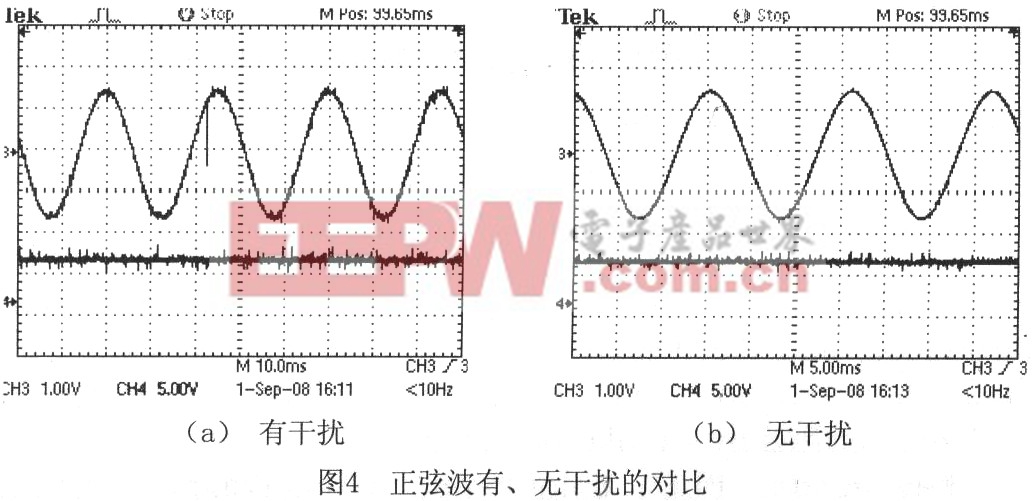

在整個電路系統中,電磁干擾主要出現在輸入與輸出接口處,其內部結構一般不會出現電磁干擾。本系統對輸入輸出信號進行接口保護,防止電磁干擾的產生;并采用線性電源及電源濾波模塊,關鍵模塊均進行電磁屏蔽,以最大程度降低模塊問的互擾。如圖3所示,左側為有電磁干擾的正弦波,可以很明顯地看出,在正弦波波峰位置突然出現一個下拉電平,經過多次分析,此現象為輸入電源受到嚴重干擾而引起,右側為經過II濾波模塊后的波形。

4 結束語

本文應用FPGA實現了模擬/數字信號采集系統設計,異步串行數據傳輸等,并且通過多路切換開關循環采集,實現了對高速信號的采集和精確的電路設計,系統性能穩定,數據采集精度較高,抗干擾能力較強,具有很高的使用價值和良好的應用前景。經過多次長時間上電測試,能產生頻率、幅值可調的波形信號,每路波形輸出電壓基準隔離,調節精度高達1%,遠高于普通的信號源,完全滿足系統設計的要求,已成功應用于某遙測信號源。

評論