基于FPGA的多路模擬信號(hào)源設(shè)計(jì)

隨著遙測(cè)系統(tǒng)的不斷發(fā)展,系統(tǒng)復(fù)雜程度也隨之提高,因此在終端設(shè)計(jì)中,對(duì)信號(hào)源的頻率穩(wěn)定度、幅值范圍和頻率范圍提出了越來越高的要求。這就要求遙測(cè)系統(tǒng)具備高碼速、實(shí)時(shí)可重構(gòu)、處理復(fù)雜結(jié)構(gòu)的能力,傳統(tǒng)的數(shù)字電路難以實(shí)現(xiàn)這些復(fù)雜功能。FPGA(現(xiàn)場(chǎng)可編程門陣列)是近幾年發(fā)展起來的硬件可編程芯片,具有硬件密度高、結(jié)構(gòu)靈活、可編程、加密性強(qiáng)等良好性能,在高速信號(hào)處理領(lǐng)域占有至關(guān)重要的地位,也為多路模擬量信號(hào)源的實(shí)現(xiàn),提供了有效的途徑。本文針對(duì)遙測(cè)應(yīng)用,以大容量FPGA器件為核心,實(shí)現(xiàn)了電源獨(dú)立的不同頻率、不同波形的多路模擬量信號(hào)源。

1 系統(tǒng)硬件設(shè)計(jì)

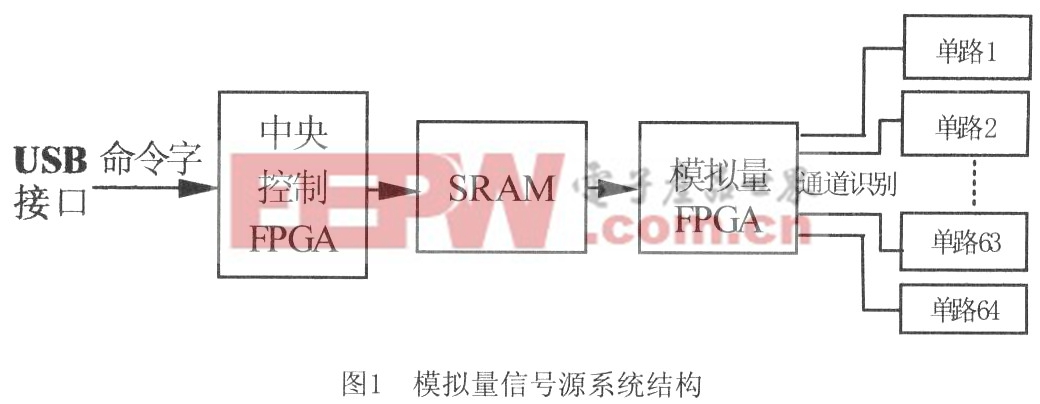

目前,大容量的FPGA主要有Altera、Xilinx、Lattice、Actel、Cypress等公司的產(chǎn)品。比較而言,Altera CycloneII系列FPGA芯片速度快、容量大、內(nèi)嵌RAM多、并且有DSP硬件乘法器,是低成本、低功耗應(yīng)用的最佳選擇。因此在本文中選用Altera公司的Cyclone II系列FPGA-EP2C8芯片,EP2C8芯片是1.25 V內(nèi)核供電,具有8.256個(gè)邏輯單元(LE),36個(gè)M4K RAM塊,RAM總量為165,888,18個(gè)嵌入式乘法器以及208個(gè)管腳,其中包括182個(gè)最大可用I/O引腳。Altera公司有相應(yīng)的開發(fā)軟件平臺(tái)Quartus II,此軟件功能強(qiáng)大,使用簡(jiǎn)單,支持的器件種類眾多,可支持在線仿真,在線下載等,并具有豐富的IP核及邏輯功能模塊資源,便于使用VHDL+模塊/原理圖輸入界面等等。模擬量信號(hào)源主要包括中央控制FPGA單元、模擬量FPGA、靜態(tài)存儲(chǔ)SRAM、單路模擬量單元,如圖l所示,

整個(gè)系統(tǒng)使用USB 2.0接口與計(jì)算機(jī)進(jìn)行通訊,信號(hào)由計(jì)算機(jī)軟件生成波形數(shù)據(jù),通過USB口下載到主控FPGA,經(jīng)過16位SRAM鎖存,將各路信號(hào)傳至模擬量FPGA,經(jīng)由解碼分路選通,輸出電源獨(dú)立的不同頻率、不同波形的多路模擬量信號(hào)。其中包括4路單極性幅值O~30V,60路雙極性幅值±15V;四種波形分別為鋸齒波、正弦波和方波(占空比1:1),信號(hào)頻率為0~50Hz,以及固定電平,幅值可以初始設(shè)定,并可實(shí)現(xiàn)實(shí)時(shí)可調(diào)。

2 單路模擬量組成模塊設(shè)計(jì)

2.1 系統(tǒng)構(gòu)成

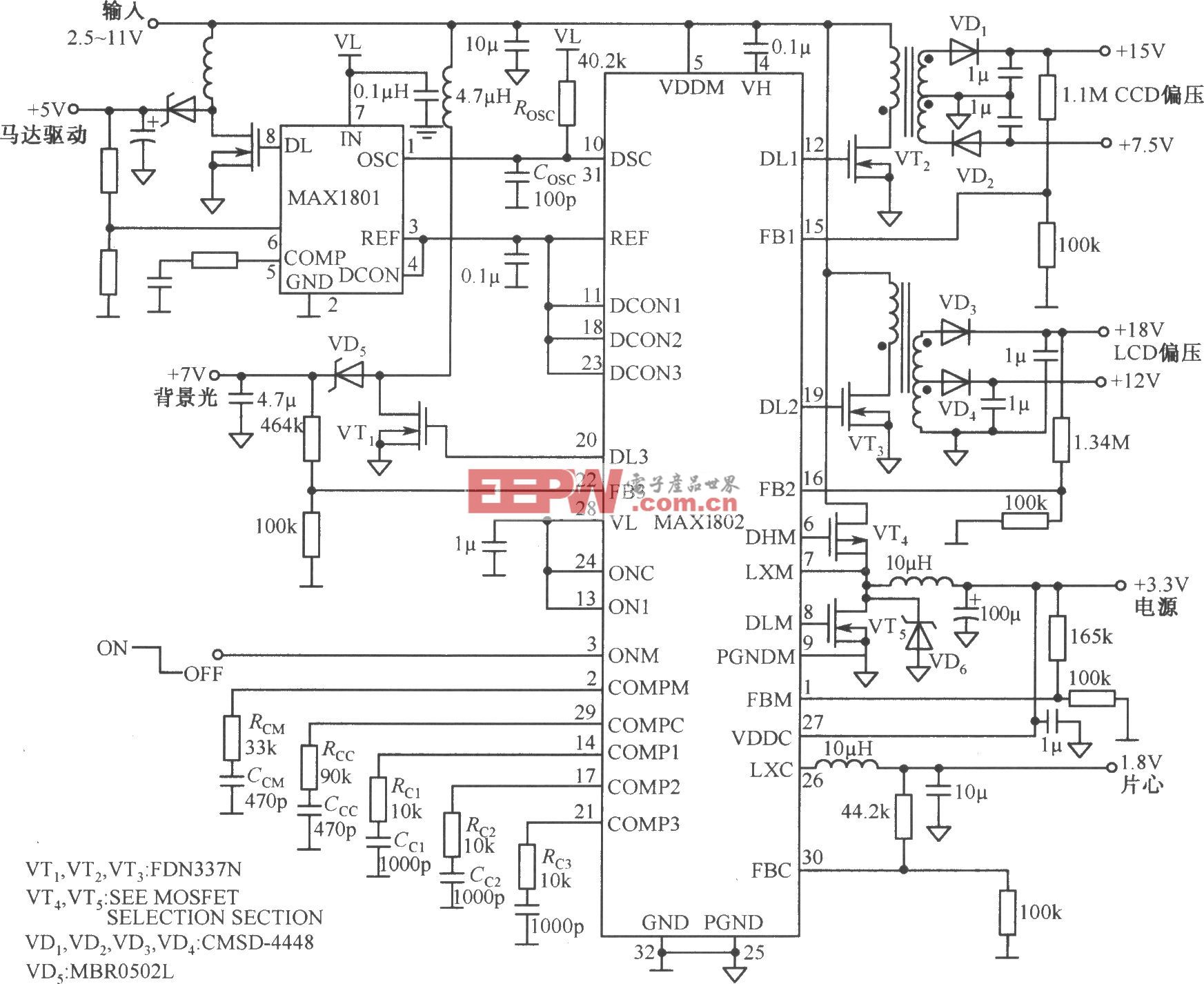

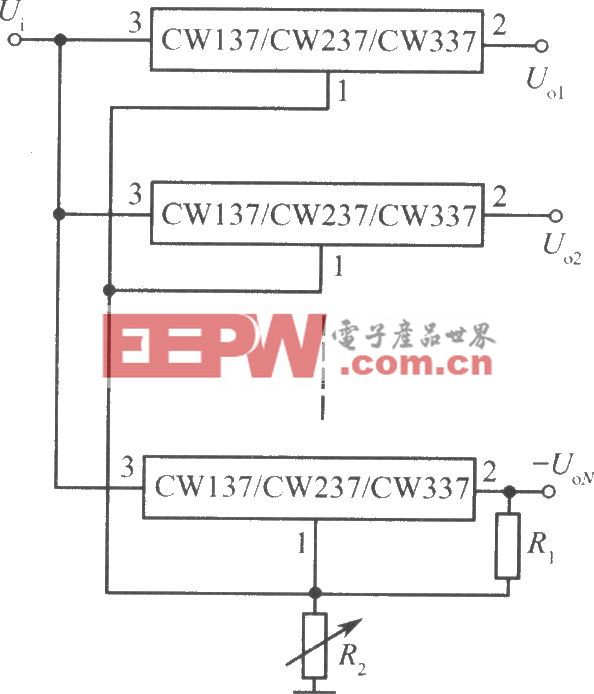

單路模擬量由電源隔離單元、前端穩(wěn)壓?jiǎn)卧?shù)模轉(zhuǎn)換(DAC)單元和運(yùn)算放大單元等構(gòu)成,具體構(gòu)成如圖2所示,系統(tǒng)由雙18 V供電經(jīng)過穩(wěn)壓?jiǎn)卧敵?.096 V,給DAC和運(yùn)放芯片提供工作電壓,另外通過指令啟動(dòng)信號(hào)在SPI總線上發(fā)送FPGA的CS、SCK、SDI信號(hào),傳至單路模擬量,將相應(yīng)數(shù)字量進(jìn)行D/A轉(zhuǎn)換,得到的模擬量數(shù)據(jù)經(jīng)由運(yùn)算放大輸出,即可實(shí)現(xiàn)64路模擬量波形。系統(tǒng)時(shí)鐘同步輸出,具有很高的可靠性。

2.2 組成模塊設(shè)計(jì)

2.2.1 電源隔離單元

64路模擬量信號(hào)要求對(duì)每路信號(hào)進(jìn)行獨(dú)立電源隔離,本文采用的ADUM1300是基于ADI公司磁耦隔離技術(shù)的通用型三通道數(shù)字隔離器,經(jīng)過自制高壓隔離信號(hào)調(diào)理電路,可以輸出系統(tǒng)任務(wù)要求的相互隔離的、獨(dú)立基準(zhǔn)模擬量信號(hào),實(shí)現(xiàn)SPI接口和數(shù)字轉(zhuǎn)換器的隔離。它采用了高速CMOS工藝和芯片級(jí)的變壓器技術(shù),在性能、功耗、體積等各方面都有光電隔離器件無法比擬的優(yōu)勢(shì)。ADUM130數(shù)字隔離器在一個(gè)器件中提供三個(gè)獨(dú)立的隔離通道,兩端工作電壓為2.7V~5.5V,支持低電壓工作,并能實(shí)現(xiàn)電平轉(zhuǎn)換。另外,ADUM130具有很低的脈寬失真(3ns),功耗僅為0.8mA,工作電壓為3V/5V,傳輸速率為1M/25M/90Mb/s,ADuM130還具有直流校正功能,有一個(gè)刷新電路保證即使不存在輸入跳變的情況下,輸出狀態(tài)也能與輸入狀態(tài)相匹配,這對(duì)于上電狀態(tài)和具有低數(shù)據(jù)速率的輸入波形或恒定的直流輸入情況是很重要的。

評(píng)論