基4-FPGA的大動態范圍數字AGC的實現

1 引言

在數字中頻接收機中,把A/D轉換提前到中頻部分,為保證A/D轉換的動態范圍和系統帶寬,要求低噪聲放大器和自動增益控制AGC(Automatic Gain Control)電路能夠提供大動態范圍的自動增益控制。AGC系統由可變增益放大器和反饋回路組成。反饋回路從可變增益放大器的輸出中提取幅度自動調節可變增益放大器的增益,當輸入可變增益放大器的信號幅度增大時,反饋回路控制其增益按一定關系減小;減小時,其增益則按一定關系增大。這樣無論輸入信號的強弱,經AGC放大后都能得到電平基本恒定的輸出信號,從而保證系統的動態范圍。數字AGC的反饋部分由數字處理實現,與模擬AGC相比,降低調試難度而且增強了穩定性、收斂性和精確性。

2 數字AGC的原理與設計

采用ADI公司的可變增益放大器、數字可控增益放大器和FPGA實現大動態范圍的自動增益控制,這兩個增益放大器均采用ADI公司的先進工藝技術,且能提供精確的線性放大,受溫度影響很小。

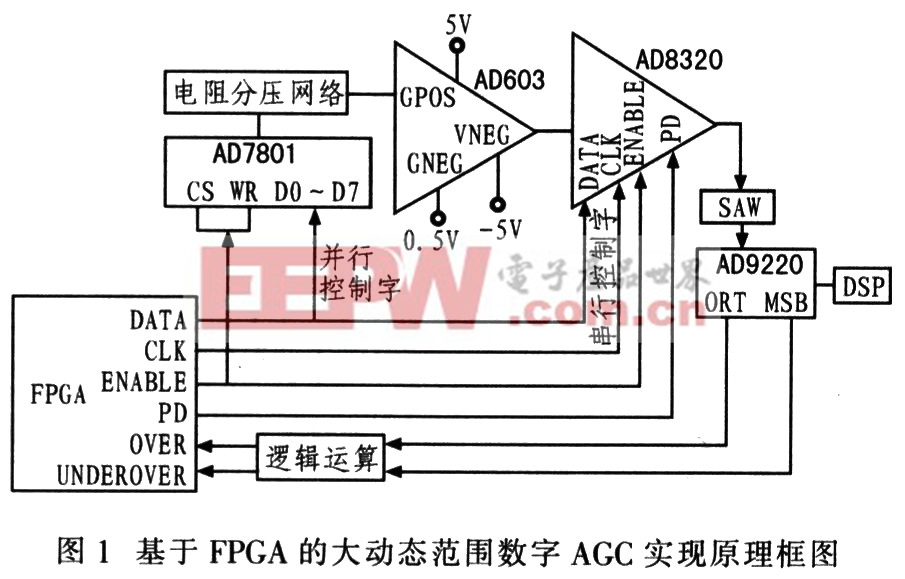

圖1為數字AGC系統原理框圖,包括可變增益放大器AD603、數字可控增益放大器AD8320、A/D轉換器AD9220、D/A轉換器AD7801,而FPGA用于實現串行轉并行以及根據AD9220的ORT指示引腳進行大動態范圍的自動增益控制。

圖1中,AD603是電壓可控增益放大器,增益由GPOS和GNEG引腳電壓差確定。當GNEG=0.5V,GPOS在0~1 V變化時,AD603增益為-lO~30 dB,增益線性變化率為25 mV/dB。AD7801是8 bit D/A轉換器,其8 bit控制寄存器由FPGA控制CS和WR信號寫入,為AD603的GPOS端口提供增益控制電壓,輸出電壓為0~2.5 V。通過電阻網絡后輸出電壓變為0~1 V,實現AD603的增益可控。AD8320是數字可控增益放大器,具有一個8 bit串行輸入控制端口,可實現256個可編程增益設置,增益與8 bit串行控制字Code的關系為:

Gain(dB)=20log10(0.077×Code+0.316) (1)

式中,Code的范圍為0~255。

評論