基于FPGA的多通道數據采集系統設計

最常用的數據采集方案多以MCU為核心,控制多路信號的采集及處理。但由于單片機本身的指令周期以及處理速度的影響,對于多通道A/D進行控制及數據處理,普通的MCU往往不容易達到要求。考慮到FPGA器件的高集成度、內部資源豐富、特別適合處理多路并行數據等明顯優于普通微處理器的特點,并針對大地電磁數據采集系統對實時性和同步性的要求,本文提出了一種多通道數據采集方案。采用FPGA與ARM相結合的設計,采集主控制邏輯用FPGA實現,ARM用來實現采集數據的存儲和數據傳輸控制。

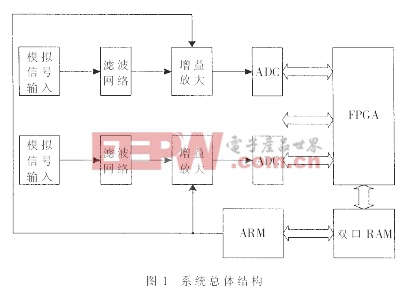

1 系統總體結構

系統總體結構如圖1所示。A/D轉換器采用TI公司的24位高精度模數轉換器ADS1255;FPGA采用Altera公司的EP2C35;ARM為ARM9內核的處理器S3C2410。雙口RAM由EP2C35內部存儲器塊配置而成,該雙口RAM與ARM的系統總線相連,映射為ARM的一塊內存區。

AD前端處理電路的作用是實現對信號的放大、衰減以及阻抗匹配,從而滿足ADC對輸入信號的要求。濾波網絡濾除高頻噪聲和工頻信號的干擾,增益放大通過ARM給出的控制信號實現對模擬信號的不同增益的放大處理。ADS1255負責把模擬電信號轉換成數字信號,可以通過功能選擇設置ADS1255工作在不同的工作模式下。ADS1255的工作時鐘由FPGA提供,改變FPGA輸出時鐘的頻率就能實現AD采樣率的改變。FPGA并行控制5路AD的數據采集,并把采集到的各路數據按順序以字節的形式寫入雙口RAM中緩存。FPGA對雙口RAM的數據寫入和ARM對數據的讀取是通過乒乓傳輸結構實現的。當FPGA寫滿雙口RAM上半區后,向ARM申請中斷,ARM響應中斷后,讀出上半區數據到內存中進行存儲;同時FPGA向RAM的下半區寫數據,寫滿下半區后也向ARM發出中斷,通知ARM讀出下半區數據。通過乒乓傳輸保證了系統數據采樣和數據傳輸可以連續進行。

2 FPGA的邏輯設計

本方案中的數據采集流程如下:系統初始化后,ARM通過控制信號把采樣頻率、通道選擇等參數通知給FPGA,然后FPGA向需要同步采樣的通道對應的AD芯片提供統一時鐘,使得AD同步地選擇相應的通道進行數據的同步采樣和轉換,其結果由FPGA接收并存儲在雙口RAM對應的存儲空間,然后由ARM從相應的雙口RAM空間讀取數據進行本地存儲或經過網絡傳輸給上位機進行處理。根據以上流程以及FPGA要實現的功能,整個FPGA邏輯設計劃分為通道和采樣率選擇模塊、時鐘模塊、雙口RAM模塊、AD采樣控制模塊、串并轉換模塊、數據存儲控制模塊、ARM接口控制模塊。

各模塊連接關系如圖2所示。

評論