基于DSP Builder的16階FIR濾波器實現

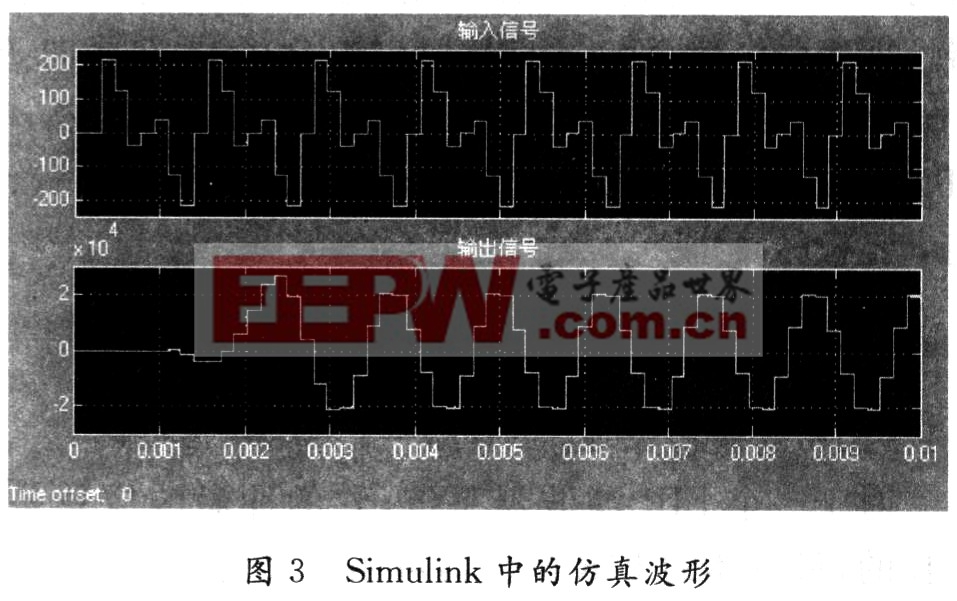

完成模型設計之后,可以先在Simulink中對模型進行仿真,可以通過Simulink中的示波器模塊查看各個步驟的中間結果。輸入信號采用800 Hz和1 600 Hz,幅值相同的兩個正弦信號的疊加。仿真結果如圖3所示。從仿真波形可以看出,通過濾波器之后,1 600 Hz的信號能夠被很好地濾除。

本文引用地址:http://www.104case.com/article/188501.htm

雙擊SignalCompiler可對以上的設計模型進行分析,選擇相應的芯片,將以上設計模塊圖文件“翻譯”成VHDL語言。

2.2.4 Modelsim的RTL仿真

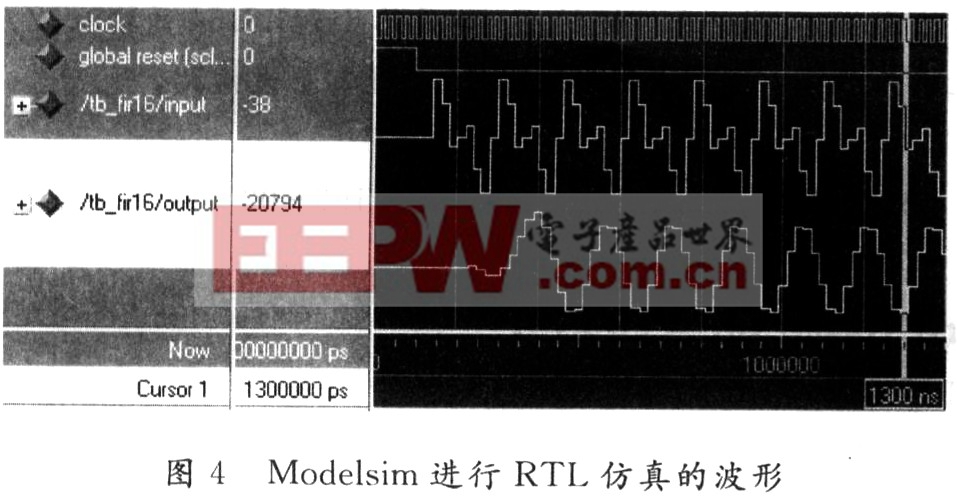

在Simulink中進行的仿真屬于系統驗證性質的,是對mdl文件進行的仿真,并沒有對生成的VHDL代碼進行仿真。事實上,生成VHDL描述的是RTL級的,是針對具體的硬件結構,而在Matlab的Simulink中的模型仿真是算法級的,兩者之間有可能存在軟件理解上的差異,轉化后的VHDL代碼實現可能與mdl模型描述的情況不完全相符。這就需要針對生成的RTL級VHDL代碼進行功能仿真,仿真結果如圖4所示。

仿真結果說明,在Modelsim中仿真結果和Simulink里的仿真結果基本一致,該濾波器有較好的濾波效果。可以看出,輸入正弦波經過數字化過程以后,能夠在Modelsim中還原出模擬波形.符合設計的要求,可以在QLtortusⅡ的環境下進行硬件設計。

2.2.5 濾波器在FPGA上的實現

在QuartusⅡ環境中,打開DSP Builder建立的QuartusⅡ項目文件,在QuartusⅡ中再進行一次仿真,由此可以看到符合要求的時序波形。然后指定器件引腳,并進行編譯,最后下載到FPGA器件中,就可以對硬件進行測試,加上clok信號和使能信號,用信號發生器產生所要求的兩個不同頻率的正弦信號,就可以在示波器上看到濾波后的結果。需要設計不同的濾波器電路是僅修改FIR濾波器模型文件就可以實現,這樣不僅避免了繁瑣的VHDL語言編程,而且便于進行調整。

3 結 語

在利用FPGA進行數字濾波器開發時,采用DSPBuilder作為設計工具,能加快進度。當然,在實際應用中,受精度、速度和器件選擇方面的影響,可能對其轉化的VHDL進行進一步的優化。

評論