基于AD9852的基準源設計

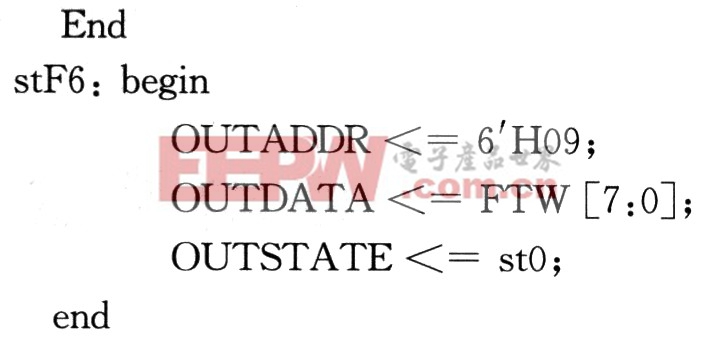

整機上電復位后,為設置某一幅值,需要將幅度控制字從高位至低位依次以并行方式寫入AD9852的地址21h、22h,VreilogHDL程序代碼如下:本文引用地址:http://www.104case.com/article/188481.htm

2.4 AM設計

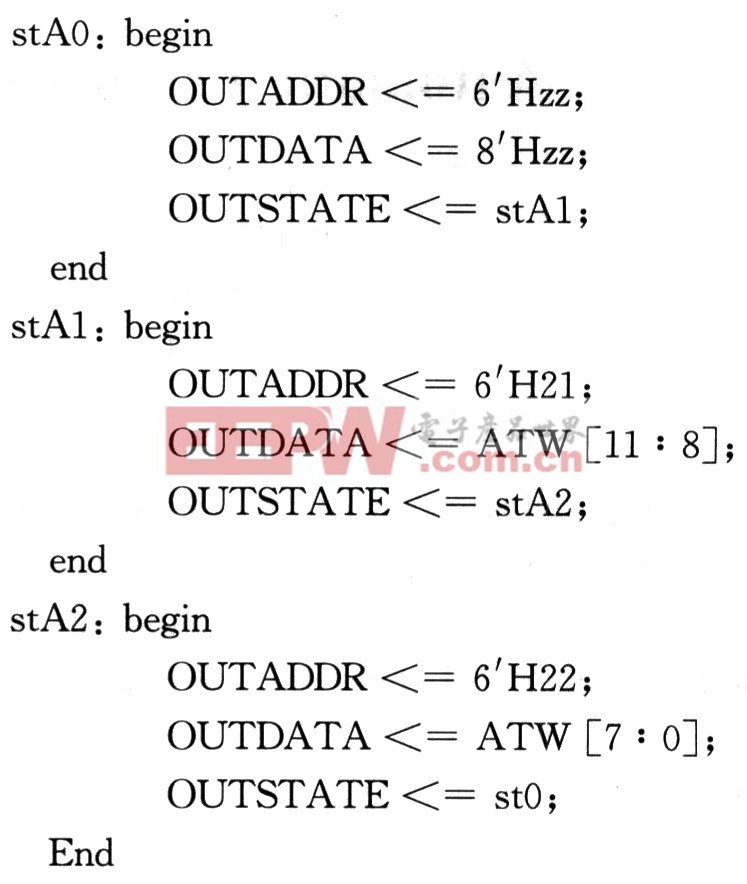

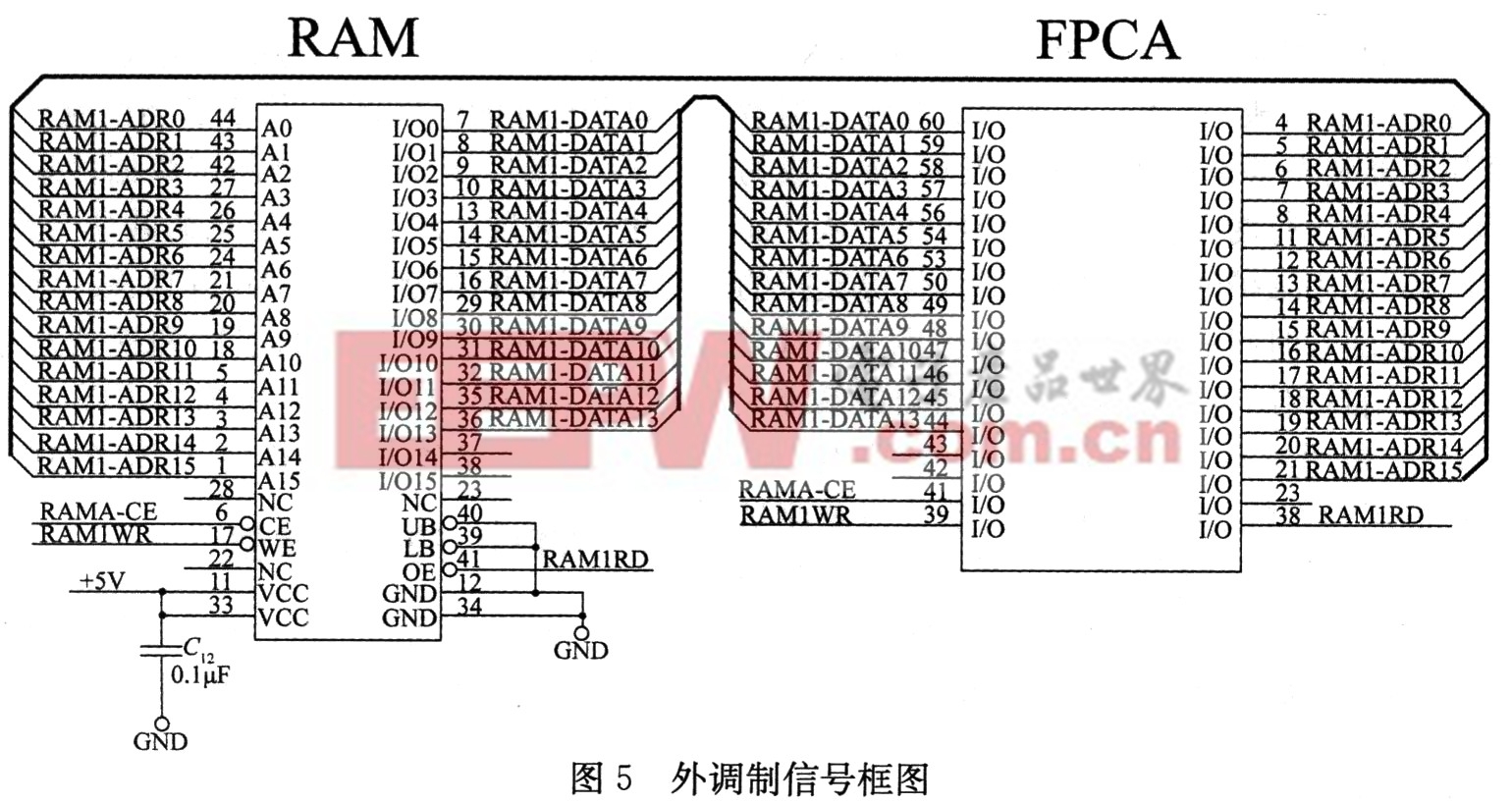

基于2.3討論的幅度控制設計,加入外調制信號可進一步實現AM調制,其中,外部調制信號的產生框圖如圖5所示:

圖5中,RAM存儲外調制信號波形,本文中需要存儲正弦波波形,由RAM和FPGA共同構建NCO。存儲的數值由上位機計算得出,并通過FPGA寫入RAM中。RAM中的數據被FPGA讀出后,由數字乘法器對其進行放大,乘系數因子由AM的調幅深度決定。向AD9852的地址21h、22h(幅度控制寄存器)寫入外部調制信號所對應的波形數據,即可實現調制速率、調制深度均可控的AM調制。

2.5 波形輸出設計

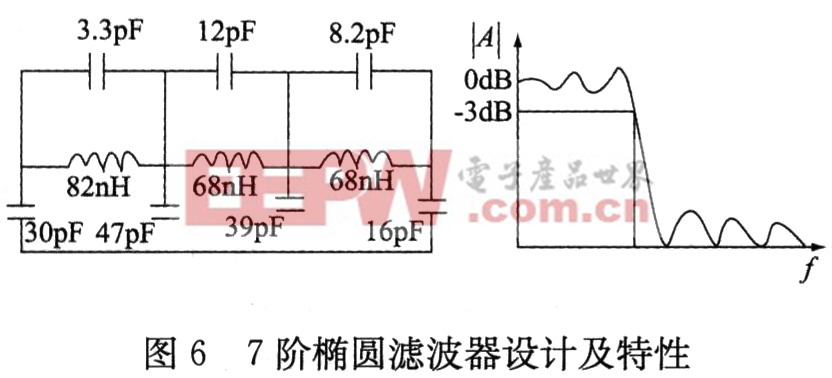

AD9852所產生的信號直接由器件內部的余弦DAC輸出,內部不含低通濾波器,故要對其輸出信號進行濾波處理。本文中,為了降低AD9852內部系統時鐘的干擾,采用了具有下降速度更快、且較窄過渡帶特性的7階橢圓濾波器。如圖6所示。

AD9852輸出信號的幅度范圍較小,需要根據實際應用情況進行放大處理,本文采用運算放大器LM7171搭建負反饋放大電路。

3 結束語

本文介紹了基準源的設計方法,采用DDS技術,具有頻率分辨率高、相位連續、低相噪低雜散等優點。基準源的頻率、幅度均可控。同時,論述了AM的實現方法,相對于傳統模擬方式的設計方法,更加輕便、小巧,且線性度良好,便于校準和批生產。該DDS已使用于便攜式信號源中,經實測整機系統運行穩定,在總參某項目中得到實際應用,達到了預期的目標,具有推廣價值。

評論