基于AD9852的基準源設計

0 引 言

直接數字頻率合成(DD6)是一種以固定的精確時鐘源為基準,利用數字處理模塊產生頻率和相位均可調的輸出信號的技術。隨著超大規模集成電路和微電子技術的發展,現代高性能、高集成度和小體積的DDS產品正快速取代傳統的模擬信號頻率合成技術,成為了這類問題新的解決方案。本文利用FPGA計算出相應的頻率控制字,并對DDS芯片AD9852進行編程,最終得到所要求的輸出波形。

1 系統總體方案設計

基準源主要由上位機控制、FPGA控制、DDS、參考源、調制信號源及波形輸出模塊組成,如圖1所示。上位機控制單元是由計算機通過USB總線連接至電路板進行控制操作。FPGA控制單元實現與上位機控制單元交互信息,同時以并行方式向DDS芯片發送控制字,以管理其內部寄存器。參考源為DDS提供高精準的時鐘晶振,確保DDS輸出信號的頻譜純度。調制信號單元為DDS提供外部調制信息。波形輸出模塊由低通濾波器、運算放大器及電阻網絡組成,主要完成DDS輸出信號的濾波,放大等功能。

系統上電復位后,電路板上的綠色LED二極管閃爍提示整機處于正常狀態。當有DDS波形輸出時,電路板上的藍色LED二極管閃爍提示工作正常。

2 系統模塊設計

2.1 系統軟件設計

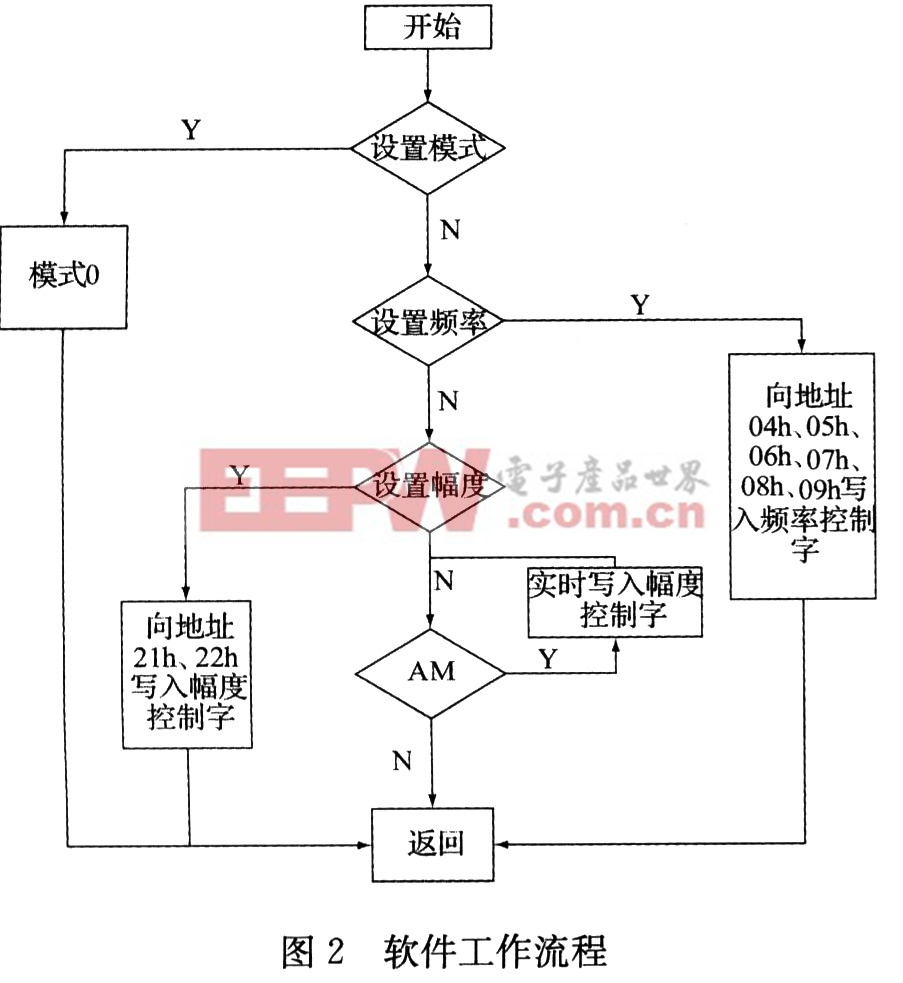

基準源的上位機控制采用C語言編程實現,主要完成對FPGA內部寄存器的讀寫操作,進而控制板上各種硬件資源的管理。另外,DDS的頻率控制字的計算也由上位機軟件計算得到。FPGA接收到上位機的命令,經解析后向DDS的內部寄存器寫入控制字,完成相應功能。同時,FPGA負責電路板上的各種時鐘管理。系統軟件的總體工作流程如圖2所示。

2.2 頻率控制設計

本文采用DDS技術產生頻率可調的波形,具有頻率分辨率高,相位連續等優點。DDS基本框圖如圖3所示。

DDS的基本結構包括:相位累加器,正弦查找表ROM,數模轉換器DAC等。DDS有兩個主要缺點:一是輸出頻率低,二是輸出頻譜中雜散多。輸出頻率低主要受DDS工作頻率的限制,隨著微電子技術的發展,這個缺陷會逐漸得到彌補。DDS輸出頻譜中的雜散是DDS所固有的,這是由DDS的工作方式決定的。

評論