基于DDS的信號模擬器設計

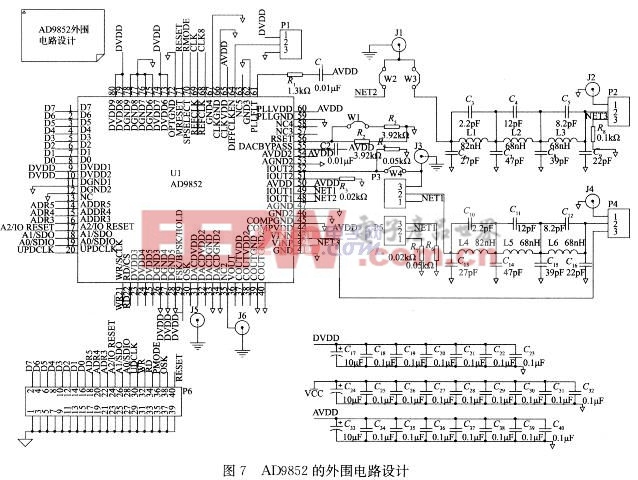

圖7為在DDS的信號發生器中AD9852的外圍電路設計。本文引用地址:http://www.104case.com/article/188298.htm

2 測試結果

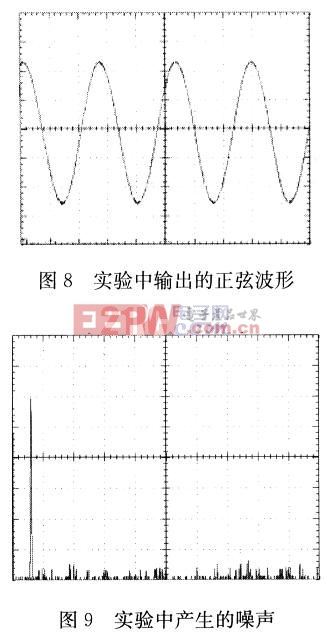

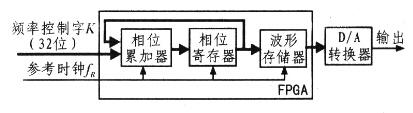

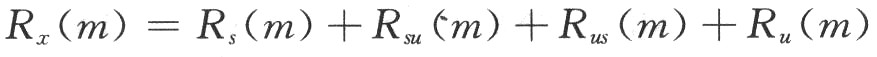

本文設計的DDS信號模擬器輸出最大頻率受到D/A轉換器輸出建立時間的限制,因為外接存儲器的數據讀取時間為15 ns,可編程邏輯器件FPGA的最大時鐘頻率可達120 MHz。相位累加器的字長為31位,用于尋址波形數據存儲器的地址信號為13位;編程產生的正弦波的輸出的頻率范圍是0~120 MHz。其中產生的正弦波如圖8所示,但是隨著時間的增長,噪聲會加大如圖9所示。

3 結束語

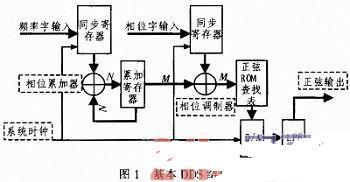

本文結合DDS信號模擬器的工作原理從理論和實際2個方面,對直接數字頻率合成技術(DDS)進行了研究。

首先通過對DDS信號模擬工作理論分析,再通過對DDS射頻信號產生電路的研究實驗使得微波信號和變頻信號在微波變頻器上混頻,產生載頻信號,再者使得調制包絡信號和調制脈沖對載頻信號進行調制,形成雷達信號,然后經天線輸出。最后結合理論分析的結論,通過測試實驗得出了系統的性能以及帶寬線性調頻和帶寬10點跳頻的過程最終輸出了雷達視頻脈沖輸出波形,基本實現了設計的要求。

評論