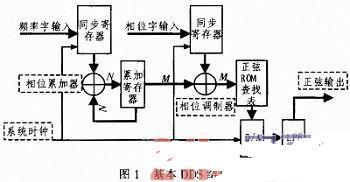

基于DDS的信號模擬器設計

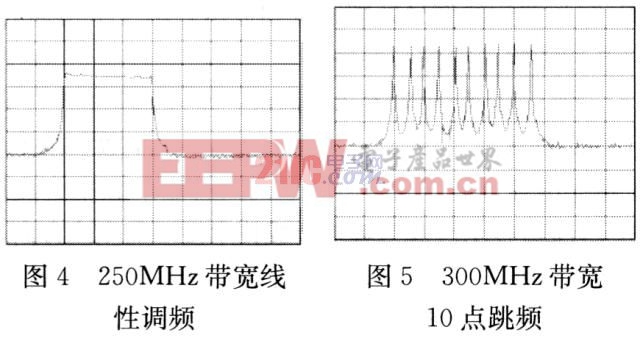

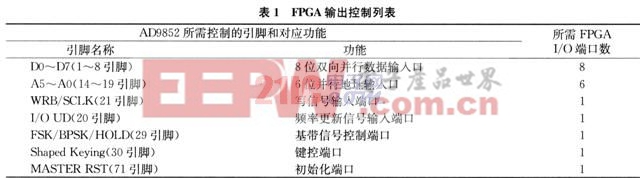

第2路是由DDS調頻及頻率捷變信號產生器產生各種調頻(普通調頻、線性調頻和非線性調頻等)和頻率捷變信號,DDS工作模式為單音頻工作模式時,通過改寫頻率控制字可實現跳頻和頻率捷變和頻率調制,工作模式為線性調頻模式時,通過設定起始頻率、頻率部進和掃描時間,可實現線性調頻。

第3路是由DDS編碼及調制波形產生器產生各種編碼和調制信號,DDS的一個顯著的特點就是在數字處理器的控制下能夠精確而快速地處理頻率和相位。DDS允許用戶對通過改寫相位偏移控制字可實現相位的任意控制,碼元的產生完全由軟件靈活控制,可產生包括二相編碼(巴克碼、偽隨機碼)、多相制編碼等,并經倍頻、濾波和放大后形成調制包絡信號。

最后來自第l路微波信號和第2路的變頻信號在微波上變頻器混頻,產生載頻信號,來自第3路的調制包絡信號和脈沖產生器產生的調制脈沖對載頻信號進行調制,形成雷達信號,最后經天線輸出。圖4、圖5為最后輸出的波形。本文引用地址:http://www.104case.com/article/188298.htm

1.6 DDS硬件設計

1.6.1 硬件電路的組成

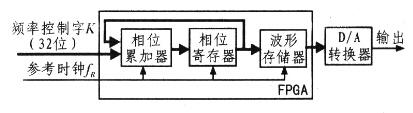

圖6為DDS模擬器硬件電路的組成原理。該信號模擬器主要由6個部分組成:電源電路、串行接口電路、下載電路、FPGA控制電路、AD9852外圍電路以及濾波電路。

1.6.2 AD9852外圍電路

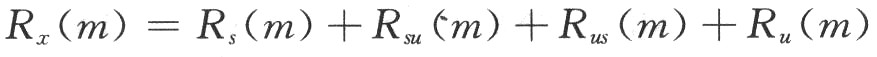

如表1所示,在并行工作模式下,FPGA主要實現對AD9852以下各引腳的控制。

AD9852內部包括1個具有48位相位累加器、1個可編程時鐘倍頻器、1個反sinc濾波器、2個12位300 MHzDAC、1個高速模擬比較器以及接口邏輯電路。其主要性能特點如下:

(1)高達300 MHz的系統時鐘;

(2)能輸出一般調制信號,FSK、BPSK、PSK、CHIRP、AM等;

(3)100 MHz時具有80 dB的信噪比;

(4)內部有4*到20*的可編程時鐘倍頻器;

(5)2個48位頻率控制字寄存器,能夠實現很高的頻率分辨率。

(6)2個14位相位偏置寄存器,提供初始相位設置。

(7)帶有100 MHz的8位并行數據傳輸口或10 MHz的串行數據傳輸口。

評論