基于3GHz CMOS低噪聲放大器優化設計

4 電路仿真與版圖設計

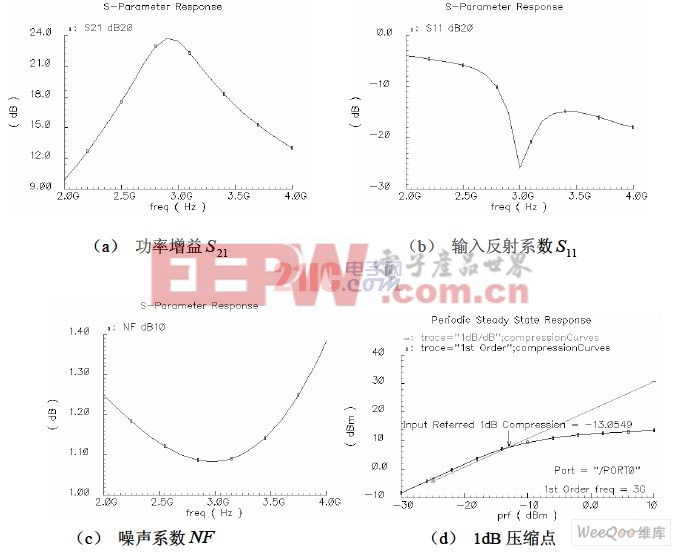

仿真采用TSMC的0.18 μm CMOS工藝,仿真環境為Cadence SpectreRF,電源電壓為2V。仿真結果如圖5所示。

從圖5(a)可以看出,所設計低噪聲放大器的功率增益在3 GHz處達到了23.4 dB,很好地滿足了功率增益的要求。圖5(b)中,輸入反射系數S11達到-25.9 dB,顯示了良好的輸入阻抗匹配。圖5(c)表明,經過噪聲優化,電路的噪聲系數只有1.1 dB,而圖5(d)中的1dB壓縮點為13.05 dBm,說明該低噪聲放大器具有良好的線性度。

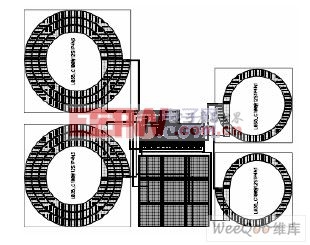

利用0.18 μm CMOS工藝模型,用cadence virtuoso軟件對LNA進行版圖設計,如圖6所示,版圖尺寸為0.485 mm × 0.395 mm。

5 結 論

本文通過對共源共柵結構的分析,從阻抗匹配、噪聲系數和線性度的角度對電路的性能進行優化,設計出了一種3 GHz的低噪聲放大器。在0.18 μm CMOS工藝下,利用Cadence SpectreRF軟件對電路進行了仿真,結果顯示,LNA的功率增益、阻抗匹配、噪聲系數和線性度等參數都達到了良好的性能。最后對LNA進行了版圖設計。

本文作者創新點:在分析共源共柵結構的基礎上改進了LNA的電路結構,提出了在共源共柵結構之間加電感以改善噪聲系數和并聯電容以增加輸入阻抗匹配的方法,對低噪聲放大器的設計具有一定的參考價值。

評論