一種新型高精度CMOS帶隙基準源的設計

3 仿真結果與分析

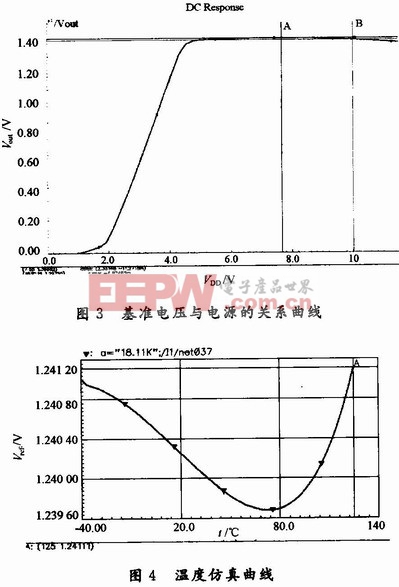

圖3說明了該基準源對電壓的抑制效果。根據仿真數據,在所取5~10 V的輸出電壓范圍經計算基準電壓電源抑制比為82 dB。圖4為Cade-nce下的溫度仿真曲線,根據所要求取的溫度范圍在-25~+120℃,計算得溫度系數為:TCF=7.427 ppm/℃。圖5為整體電路的版圖設計,面積近似為0.022 mm2。本文引用地址:http://www.104case.com/article/187781.htm

4 結語

本文通過對傳統帶隙基準源的基本原理分析,設計的基準電路工作電壓為5~10 V,通過飽和狀態MOS等效電阻對PTAT電流反饋補償,得到了82 dB的電源電壓抑制比和低于7.427 ppm/℃的溫度系數,版圖面積0.022 mm2。該電路產生的基準源電壓基本滿足普通應用要求。

評論