基于多數決定邏輯非門的低功耗全加器設計

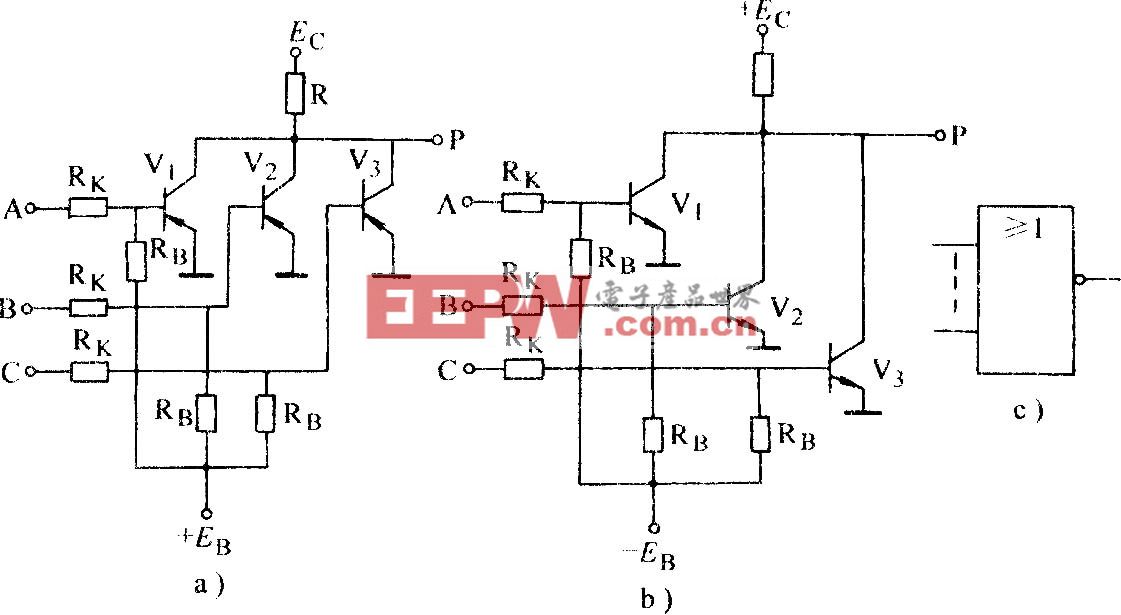

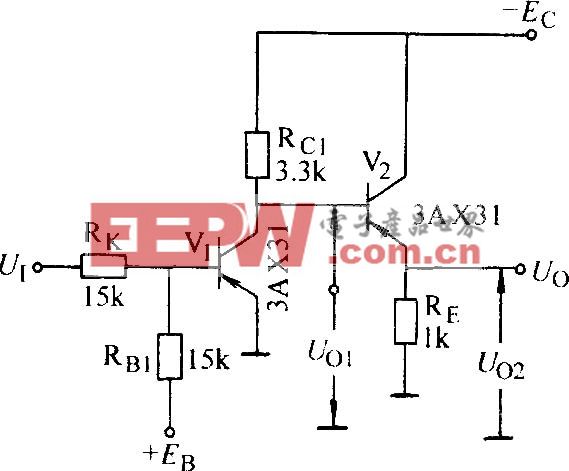

普通CMOS門電路的功耗主要由動態功耗Pswich、短路功耗Pshort、靜態漏電流功耗Pleak三部分組成,見式(1)。如果滿足式(2),則兩個管子不能同時導通,除去Pshort,功耗將顯著減小。

式中:fcp表示系統時鐘脈沖;Vim為節點i的電壓變化范圍(理想情況下為VDD);CiL為節點i的等效負載電容;ai為節點i的活動因子;Iisc和IL分別為短路電流和漏電流;P為總功耗。

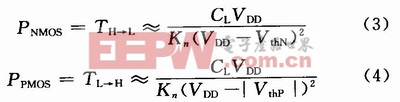

式中:VthP和VthN分別是PMOS管和CMOS管的開啟電壓。開啟電壓指的是絕緣柵場效應管(MOSFET)溝道形成時的電壓。

圖1中因為電路僅用了兩個管子,所以電源電壓可減小,相對于電源電壓,Pswich將以二次方的速度衰減。只需滿足式(2),除去Pshort。所以其功耗大大小于傳統的CMOS門電路。

雖然減小電源電壓可以減小功耗,但是會影響電路的輸出波形。式(3)、式(4)給出電源電壓的減小和開啟電壓的增大對管子高低電平轉換延遲時間的影響。

2 全加器的設計

2.1 全加器的邏輯設計

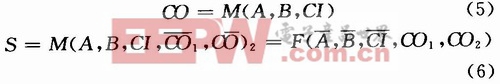

根據全加器的定義,其真值表如表1所示。其中,A和B為加數和被加數,CI為來自低位的進位;S為和輸出,CO為進位輸出。根據前面的分析,全加器的進位輸出CO可表示為輸入A,B,CI的多數決定邏輯,而和輸出S則為A,B,CI,

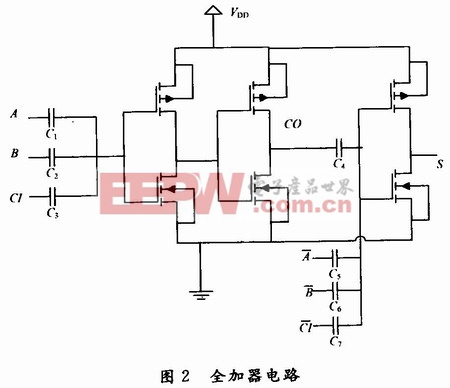

2.2 全加器的電路設計

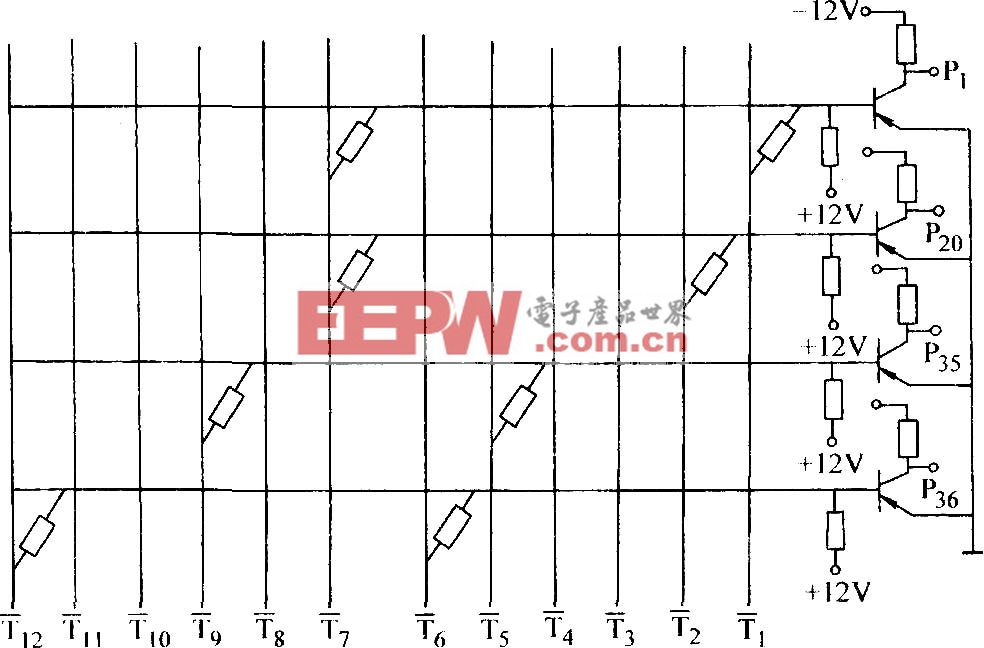

根據邏輯式(5)、式(6),設計電路如圖2所示。該設計中,僅用了兩個多數決定邏輯非門。只需6個MOSFET即可實現優化的CMOS全加器,用PSpice進行了晶體管級模擬。結果顯示,這種新的全加器能正確完成加法器的邏輯功能。圖2中,C1=C2=C3=0.05 fF,2C4=C5=C6=C7=2.88 fF。本文引用地址:http://www.104case.com/article/187763.htm

3 結語

提出一種低功耗的僅用輸入電容和CMOS反向器實現的一位全加器電路設計。該電路僅用了6個管子,從而達到降低功耗的目的。較少的管子、工作于極低電源電壓以及短路電流的消除是該全加器3個主要特征。

評論