一種基于PWM的CMOS誤差放大器的設計

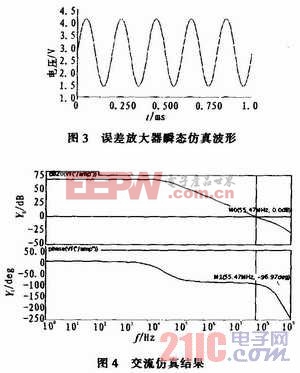

進行瞬態仿真,仿真結果如圖3所示。觀察電路波形,確認模塊實現了電壓的比較和誤差的放大功能。由瞬態仿真波形圖可以看出,輸入差模電壓為1 mV時,輸出電壓最大值可達4.15 V,最小值接近1.52 V,輸出擺幅不小于2.63 V。加大信號,可測得輸出電壓的建立時間:

計算可得上升建立時間和下降建立時間分別為6.7 V/μs和5.7 V/μs。本文引用地址:http://www.104case.com/article/187565.htm

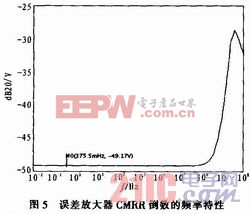

對電路進行交流增益仿真,觀察電路增益和單位增益帶寬,結果如圖4所示。

根據交流仿真結果可知,電路0 dB帶寬達到55.5 MHz,電壓開環增益約67.2 dB,相位裕度為180°-96.97°≈83.0°。

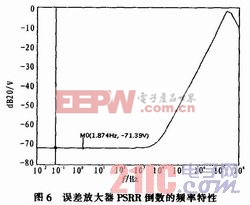

共模抑制比CMRR是放大器對輸入端共模信號的抑制能力,其計算表達式為

![]()

其中Avd表示差模增益,Avc表示共模增益。把運算放大器連接成單位增益負反饋的模式,在運算放大器的同相和反相輸入端加上相同的交流電壓,進行交流仿真,得到的仿真結果如圖5所示,該曲線是1/CMRR,因此可以得到運算放大器的低頻共模抑制比為49.17 dB。

電源抑制比PSRR是衡量電路對電源噪聲的抑制能力,把運算放大器連接成單位增益負反饋的模式,僅在供電電壓源上增加1 V的交流電壓,測試結果如圖6所示,該曲線是1/PMRR,因此運算放大器的低頻電源抑制比為71.39 dB,各項指標達到預期要求。

4 結論

為解決PWM控制器中輸出電壓與基準電壓的誤差放大問題,本文設計了一款高增益,寬帶寬,輸出擺幅可以控制的新型誤差放大器。通過在二級放大電路中間增加一級緩沖電路,克服補償電容的前饋效應,同時消除補償電容引入的零點。通過交流仿真驗證,電路0 dB帶寬達到55.5 MHz,電壓開環增益約67.2 dB,相位裕度為83.0°上升建立時間和下降建立時間分別為6.7 V/μs和5.7 V/μs,共模抑制比和電源抑制比分別為49.17 dB和71.39 dB。其突出優點是自頂向下設計,每一個器件的具體參數先通過手工計算再用軟件仿真逐步調整獲得,查找和修改錯誤方便,具有較大的靈活性。該誤差放大器已經成功運用到PWM芯片中,其獨特的結構使得PWM的最大輸出占空比和最小輸出占空比可以控制,大幅提升了芯片系統的整體性能。

pwm相關文章:pwm是什么

pwm相關文章:pwm原理

評論