雷達目標模擬器的DSP軟件設計

2.2 寬帶目標回波產生

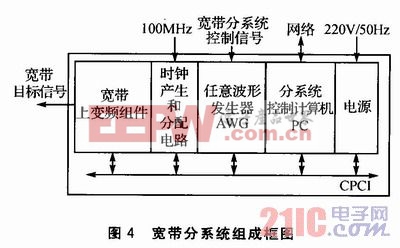

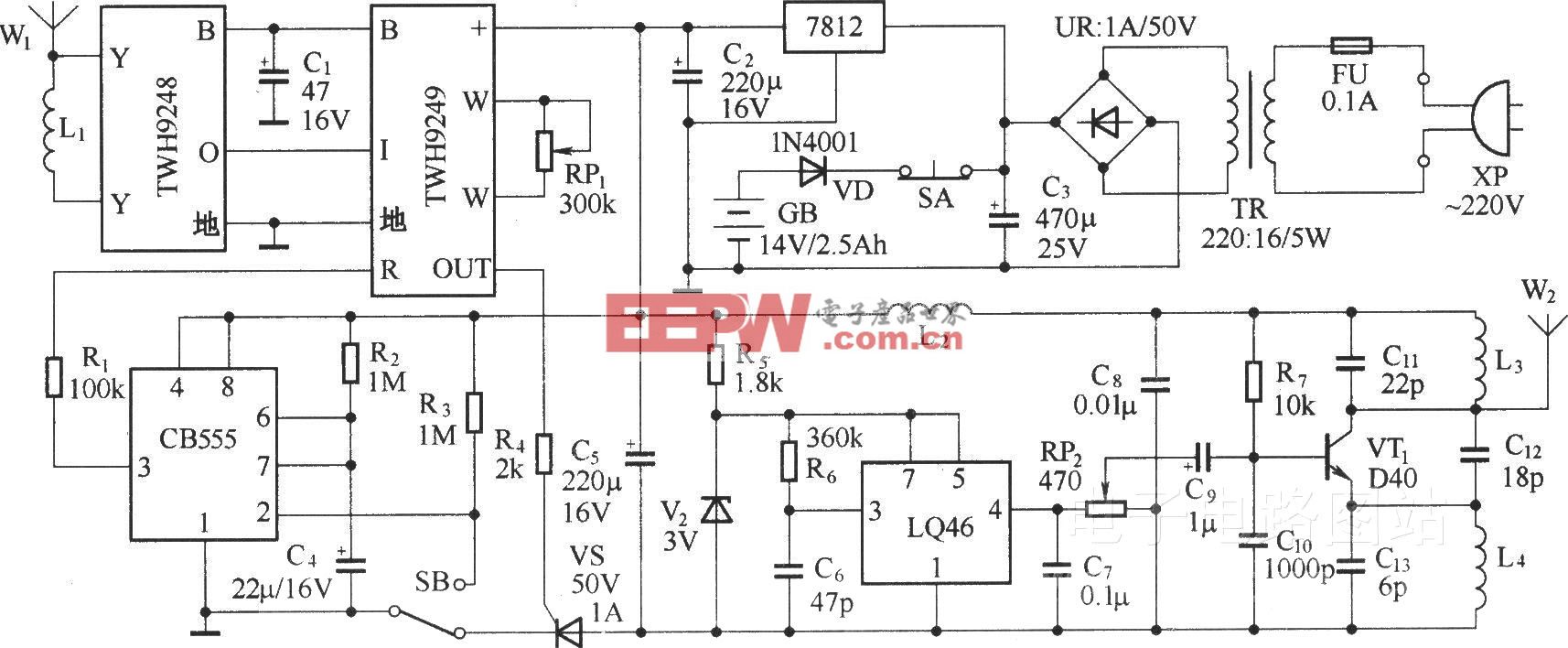

寬帶目標回波的產生通過對預先存儲在存儲器中的雷達寬帶LFM的基帶分量和目標特征參數直接計算,實時生成多散射點合成目標的波形數據實現。如圖4所示,寬帶分系統中的所有信號都與試驗雷達系統的參考信號同步,保證回波信號與雷達系統相參,實現正確的模擬。本文引用地址:http://www.104case.com/article/187423.htm

輸出寬帶目標回波信號前,在計算機上加載輸出目標散射點的運動軌跡參數和目標特性文件。當雷達系統發射寬帶LFM信號時,寬帶目標回波的基帶數據由DSP計算并加載到任意波形發生器(AWG)的存儲器中。DMU產生寬帶分系統的延時觸發脈沖和波形選擇信號,控制AwG輸出模擬基帶回波信號,將該基帶信號進行正交調制后,通過上變頻就得到寬帶信號的目標回波。目標特征數據通過CompactPCI總線加載到DSP中參與波形計算。

寬帶回波信號的更新率決定于AWG的數據更新率。這種數字方法原理簡單,模擬目標靈活,精度非常高,信號質量較高。缺點是成本較高,實時性受硬件速度、波形復雜度等限制,不容易提高。

如圖5所示,DSP模塊中有兩個TMS320C6455高性能DSP、存儲器和大規模FPGA,完成特征數據接收、波形計算更新和數據傳輸等功能,是AWG的核心控制部分。AWG模塊的FPGA采用Xilinx公司的XC4VLX25-FF668。IQ信號通路的DAC選用兩片Atmel公司的1GHz 10位TS86101G2B,且兩路DAC相互獨立且保持信號的同步。其單路瞬時帶寬可達400 MHz,與正交調制器配合可輸出復雜的調制信號。

3 系統工作流程

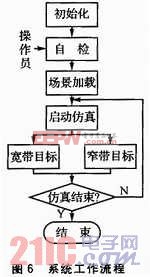

系統初始化完成后,設備進行加電自檢。自檢通過后由系統操作員進行仿真場景文件加載,包括系統參數、目標數量、軌跡、目標特性等。啟動仿真后,模擬系統中的寬帶和窄帶分系統是同時工作的,受基帶分系統中的DMU的控制,如圖6所示。

4 DSP軟件實現

4.1 基帶分系統的數字管理單元

DMU是系統的核心控制單元。DMU采用CompactPCI接口,板載總容量4百萬門的Xilinx Vhrex-2Pro FPGA,所采用的DSP為TI的TMS320C6416系列,處理器頻率為600 MHz,同時板上提供了1 GB大容量的DDR存儲器。

評論